|

|

Elastic properties of Cu-6wt% Ag alloy wires for pulsed magnets investigated by ultrasonic techniques

Ziyu Li(李滋雨), Tianyi Gu(顾天逸), Wenqi Wei(魏文琦), Yang Yuan(袁洋), Zhuo Wang(王卓), Kangjian Luo(罗康健), Yupeng Pan(潘宇鹏), Jianfeng Xie(谢剑峰), Shaozhe Zhang(张绍哲), Tao Peng(彭涛), Lin Liu(柳林), Qi Chen(谌祺), Xiaotao Han(韩小涛), Yongkang Luo(罗永康), and Liang Li(李亮)

Chin. Phys. B,

2025, 34 (2):

020701.

DOI: 10.1088/1674-1056/ada1c8

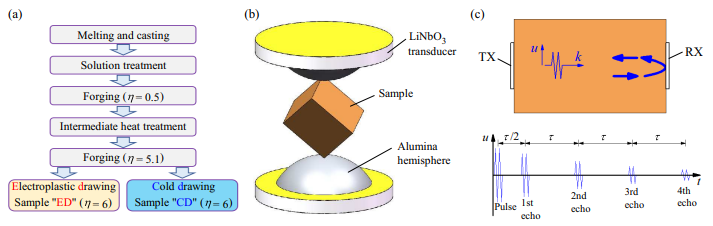

Conductor materials with good mechanical performance as well as high electrical and thermal conductivities are particularly important to break through the current bottle-neck limit ($\sim 100$ T) of pulsed magnets. Here, we perform systematic studies on the elastic properties of the Cu-6wt% Ag alloy wire, which is a promising candidate material for the new-generation pulsed magnets, by employing two independent ultrasonic techniques, i.e., resonant ultrasound spectroscopy (RUS) and ultrasound pulse-echo experiments. Our RUS measurements manifest that the elastic properties of the Cu-6wt% Ag alloy wires can be improved by an electroplastic drawing procedure as compared with the conventional cold drawing. We also take this opportunity to test the availability of our newly-built ultrasound pulse-echo facility at the Wuhan National High Magnetic Field Center (WHMFC, China), and the results suggest that the elastic performance of the electroplastically-drawn Cu-6wt% Ag alloy wire remains excellent without anomalous softening under extreme conditions, e.g., in ultra-high magnetic field up to 50 T and nitrogen or helium cryogenic liquids.

|

|