中国物理B ›› 2020, Vol. 29 ›› Issue (10): 108504-.doi: 10.1088/1674-1056/ab99b8

Wei-Tao Yang(杨卫涛)1,4, Yong-Hong Li(李永宏)1,†( ), Ya-Xin Guo(郭亚鑫)1, Hao-Yu Zhao(赵浩昱)1, Yang Li(李洋)1, Pei Li(李培)1, Chao-Hui He(贺朝会)1, Gang Guo(郭刚)2, Jie Liu(刘杰)3, Sheng-Sheng Yang(杨生胜)5, Heng An(安恒)5

), Ya-Xin Guo(郭亚鑫)1, Hao-Yu Zhao(赵浩昱)1, Yang Li(李洋)1, Pei Li(李培)1, Chao-Hui He(贺朝会)1, Gang Guo(郭刚)2, Jie Liu(刘杰)3, Sheng-Sheng Yang(杨生胜)5, Heng An(安恒)5

-

收稿日期:2020-05-07修回日期:2020-05-19接受日期:2020-06-05出版日期:2020-10-05发布日期:2020-10-05 -

通讯作者:Yong-Hong Li(李永宏)

Investigation of single event effect in 28-nm system-on-chip with multi patterns

Wei-Tao Yang(杨卫涛)1,4, Yong-Hong Li(李永宏)1,†, Ya-Xin Guo(郭亚鑫)1, Hao-Yu Zhao(赵浩昱)1, Yang Li(李洋)1, Pei Li(李培)1, Chao-Hui He(贺朝会)1, Gang Guo(郭刚)2, Jie Liu(刘杰)3, Sheng-Sheng Yang(杨生胜)5, and Heng An(安恒)5

- 1

School of Nuclear Science & Technology, Xi’an Jiaotong University , Xi’an 710049,China

2National Innovation Center of Radiation Application, China Institute of Atomic Energy , Beijing 102413,China

3Institute of Modern Physics, Chinese Academy of Sciences , Lanzhou 730000,China

4Dipartimento di Automatica e Informatica, Politecnico di Torino , Torino 10129,Italy

5Science and Technology on Vacuum Technology and Physics Laboratory, Lanzhou Institute of Physics , Lanzhou 730000,China

-

Received:2020-05-07Revised:2020-05-19Accepted:2020-06-05Online:2020-10-05Published:2020-10-05 -

Contact:†Corresponding author. E-mail:yonghongli@mail.xjtu.edu.cn -

About author:†Corresponding author. E-mail: yonghongli@mail.xjtu.edu.cn* Project supported by the National Natural Science Foundation of China (Grant Nos. 11575138, 11835006, 11690040, and 11690043), the Fund from Innovation Center of Radiation Application (Grant No. KFZC2019050321), the Fund from the Science and Technology on Vacuum Technology and Physics Laboratory, Lanzhou Institute of Physics (Grant No. ZWK1804), and the Program of China Scholarships Council (Grant No. 201906280343).

中图分类号: (Semiconductor-device characterization, design, and modeling)

- 85.30.De

引用本文

Wei-Tao Yang(杨卫涛), Yong-Hong Li(李永宏), Ya-Xin Guo(郭亚鑫), Hao-Yu Zhao(赵浩昱), Yang Li(李洋), Pei Li(李培), Chao-Hui He(贺朝会), Gang Guo(郭刚), Jie Liu(刘杰), Sheng-Sheng Yang(杨生胜), Heng An(安恒). [J]. 中国物理B, 2020, 29(10): 108504-.

Wei-Tao Yang(杨卫涛), Yong-Hong Li(李永宏)†, Ya-Xin Guo(郭亚鑫), Hao-Yu Zhao(赵浩昱), Yang Li(李洋), Pei Li(李培), Chao-Hui He(贺朝会), Gang Guo(郭刚), Jie Liu(刘杰), Sheng-Sheng Yang(杨生胜), and Heng An(安恒). Investigation of single event effect in 28-nm system-on-chip with multi patterns[J]. Chin. Phys. B, 2020, 29(10): 108504-.

| [1] |

Selma S, Rolf E, Sascha U, Henrik T, Benoît D D D 2015 International Conference on Hardware/Software Codesign and System Synthesis October 4–9, 2015 Amsterdam, Netherlands DOI: 10.1109/CODESISSS.2015.7331385

|

| [2] |

Massimo V, Cristina M, Ricardo R, Matteo S R 2011 IEEE Trans. Ind. Electron. 58 2617 DOI: 10.1109/TIE.2011.2134054

|

| [3] |

Daniel M F, Peter S W, Paul E D 2000 Microelectron. Reliab. 40 17 DOI: 10.1016/S0026-2714(99)00225-5

|

| [4] |

Bi J S, Xi K, Li B, Wang H B, Ji L L, Li J, Liu M 2018 Chin. Phys. B 27 098501 DOI: 10.1088/1674-1056/27/9/098501

|

| [5] |

Chen W, Yang H L, Guo X Q, Yao Z B, Ding L L, Wang Z J, Wang C H, Wang Z M, Cong P T 2017 Chin. Sci. Bull. 62 978 DOI: 10.1360/N972016-00438

|

| [6] |

Sexton F W 2003 IEEE Trans. Nucl. Sci. 50 603 DOI: 10.1109/TNS.2003.813137

|

| [7] |

Bi J S, Zeng C B, Gao L C, Liu G, Luo J J, Han Z S 2014 Chin. Phys. B 23 088505 DOI: 10.1088/1674-1056/23/8/088505

|

| [8] |

Luo J, Liu J, Sun Y M, Hou M D, Xi K, Liu T Q, Wang B, Ye B 2017 Nucl. Instrum. Methods Phys. Res. B 406 431 DOI: 10.1016/j.nimb.2017.04.038

|

| [9] |

Juan A C, Guillaume H, Francisco J F, Francesca V, Maud B, Hortensia M, Helmut P, Raoul V 2017 IEEE Trans. Nucl. Sci. 64 2188 DOI: 10.1109/TNS.2017.2682984

|

| [10] |

Pan X Y, Guo H X, Luo Y H, Zhang F Q, Ding L L 2018 Chin. Phys. B 27 038501 DOI: 10.1088/1674-1056/27/3/038501

|

| [11] |

Zhang K Y, Zhang F Q, Luo Y H, Guo H X 2013 Chin. Phys. B 23 028501 DOI: 10.1088/1674-1056/23/2/028501

|

| [12] |

Jin X M, Chen W, Li J L, Qi C, Guo X Q, Li R B, Liu Y 2019 Chin. Phys. B 28 104212 DOI: 10.1088/1674-1056/ab4175

|

| [13] |

Xabier I, Didier K, Patrick Y, Daniel B, Robert C, Kevin H, Emre O 2015 23th IFIP/IEEE International Conference on Very Large Scale Integration - System on a Chip (VLSI-SoC) October 5–7, 2015 Daejeon, Korea DOI: 10.1007/978-3-319-46097-0_1

|

| [14] |

Chen X Y, Gu Y, Wang C X, Guan X G 2016 International Conference on Field-Programmable Technology (FPT) December 7–9, 2016 Xi’an, China DOI: 10.1109/FPT.2016.7929570

|

| [15] |

ARM. 2017 Application Note Cortex-M33 Dual Core Lockstep

|

| [16] |

Lucas A T, Paolo R, Eduardo C, Jorge T, Fernanda L K 2016 IEEE Trans. Nucl. Sci. 63 2217 DOI: 10.1109/TNS.2016.2522508

|

| [17] |

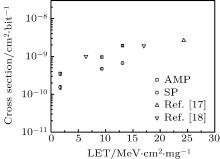

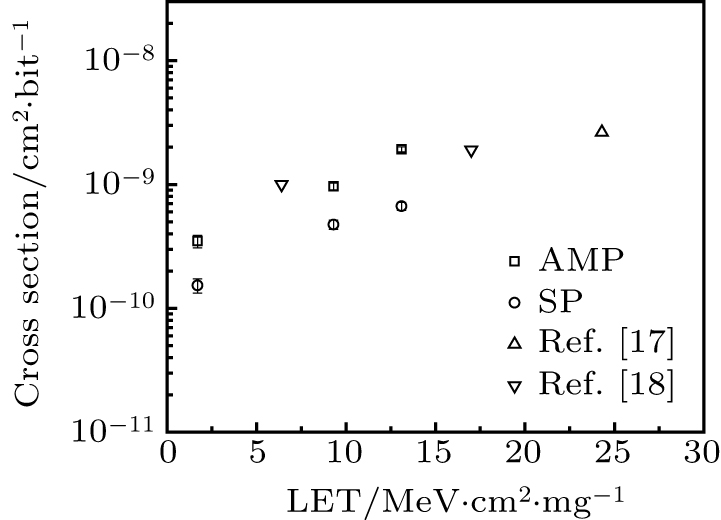

Greg A, Farokh I, Mehran A 2015 NASA Electronic Parts and Packaging Program (NEPP) Electronics Technology Workshop (ETW) June 23–26, 2015 Greenbelt, USA

|

| [18] |

Lucas A T, Fernanda L K, Nilberto H M, Nemitala A, Vitor A P A, Fernando A, Eduardo L A M, Marcilei A G S 2015 IEEE Radiation Effects Data Workshop (REDW) July 13–17, 2015 Boston, MA, USA DOI: 10.1109/REDW.2015.7336716

|

| [19] |

Mehran A, Farokh I, Steven M G, Greg A 2015 IEEE Radiation Effects Data Workshop (REDW) July 13–17, 2015 Boston, MA, USA DOI: 10.1109/REDW.2015.7336714

|

| [20] |

Du X C, He C H, Liu S H, Zhang Y, Li Y H, Yang W T 2017 J. Nucl. Sci. Technol. 54 287 DOI: 10.1080/00223131.2016.1262294

|

| [21] |

Yang W T, Du X C, He C H, Shi S T, Cai L, Hui N, Guo G, Huang C L 2018 IEEE Trans. Nucl. Sci. 65 545 DOI: 10.1109/TNS.2017.2776244

|

| [22] |

Yang W T, Du X C, Guo J L, Wei J Z, Du G H, He C H, Liu W J, Shen S S, Huang C L, Li Y H, Fan Y Y 2019 Nucl. Instrum. Methods Phys. Res. B 450 323 DOI: 10.1016/j.nimb.2018.09.038

|

| [23] |

Yang W T, Li Y H, Li Y, Hu Z L, Xie F, He C H, Wang S L, Zhou B, H. He H, Waseem K, Liang T J 2019 Microelectron. Reliab. 99 119 DOI: 10.1016/j.microrel.2019.05.004

|

| [24] |

Ádria B D O, Gennaro S R, Fernanda L K 2017 30th Symposium on Integrated Circuits and Systems Design August 28–September 1, 2017 Fortaleza, Brazil DOI: 10.1145/3109984.3110008

|

| [25] |

Adria B D O, Gennaro S R, Fernanda L K, Nemitala A, Eduardo L A M, Vitor A P A, Nilberto H M, Marcilei A G S 2018 IEEE Trans. Nucl. Sci. 65 1783 DOI: 10.1109/TNS.23

|

| [26] |

Xilinx, Inc. 2015 Zynq-7010 All Programmable SoC Overview, DS190(v1.8).

|

| [27] |

Xilinx, Inc. 2015 Zynq-7000 All Programmable SoC Technical Reference Manual, UG585 (v1.10)

|

| [28] |

SRIM (2013). Particle Interactions with Matter [Online]. Available: http://www.srim.org/

|

| [29] |

Petersen E L 2008 IEEE Trans. Nucl. Sci. 55 2819 DOI: 10.1109/TNS.2008.2007903

|

| [30] | |

| [31] |

Tylka A J, Adams J H, Boberg P R, Brownstein B, Dietrich W F, Flueckiger E O, Petersen E L, Shea M A, Smart D F, Smith E C 1997 IEEE Trans. Nucl. Sci. 44 2150 DOI: 10.1109/23.659030

|

| [32] |

Chen R, Han J W, Zheng H S, Yu Y T, Shangguan S P, Feng G Q, Ma Y Q 2015 Chin. Phys. B 24 046103 DOI: 10.1088/1674-1056/24/4/046103

|

| [33] |

David S L, Michael W, Gary S, Anthony C L 2014 IEEE Radiation Effects Data Workshop (REDW) July 14–18, 2014 Paris, France DOI: 10.1109/REDW.2014.7004595

|

| [1] | Xin-Yu Xie(谢新宇), Jian Li(李健), Xiao-Lang Qiu(邱小浪), Yong-Li Wang(王永丽), Chuan-Chuan Li(李川川), Xin Wei(韦欣). Mode characteristics of VCSELs with different shape and size oxidation apertures[J]. 中国物理B, 2023, 32(4): 44206-044206. |

| [2] | Jin-Ping Zhang(张金平), Hao-Nan Deng(邓浩楠), Rong-Rong Zhu(朱镕镕), Ze-Hong Li(李泽宏), and Bo Zhang(张波). High performance carrier stored trench bipolar transistor with dual shielding structure[J]. 中国物理B, 2023, 32(3): 38501-038501. |

| [3] | Lijian Guo(郭力健), Weizong Xu(徐尉宗), Qi Wei(位祺), Xinghua Liu(刘兴华), Tianyi Li(李天义), Dong Zhou(周东), Fangfang Ren(任芳芳), Dunjun Chen(陈敦军), Rong Zhang(张荣), Youdou Zheng(郑有炓), and Hai Lu(陆海). Demonstration and modeling of unipolar-carrier-conduction GaN Schottky-pn junction diode with low turn-on voltage[J]. 中国物理B, 2023, 32(2): 27302-027302. |

| [4] | Yuankang Chen(陈远康), Yuanliang Zhou(周远良), Jie Jiang(蒋杰), Tingke Rao(饶庭柯), Wugang Liao(廖武刚), and Junjie Liu(刘俊杰). Enhancement of holding voltage by a modified low-voltage trigger silicon-controlled rectifier structure for electrostatic discharge protection[J]. 中国物理B, 2023, 32(2): 28502-028502. |

| [5] | Jie Wei(魏杰), Qinfeng Jiang(姜钦峰), Xiaorong Luo(罗小蓉), Junyue Huang(黄俊岳), Kemeng Yang(杨可萌), Zhen Ma(马臻), Jian Fang(方健), and Fei Yang(杨霏). High performance SiC trench-type MOSFET with an integrated MOS-channel diode[J]. 中国物理B, 2023, 32(2): 28503-028503. |

| [6] | Yidan Zhang(张一丹), Chunshuang Chu(楚春双), Sheng Hang(杭升), Yonghui Zhang(张勇辉),Quan Zheng(郑权), Qing Li(李青), Wengang Bi(毕文刚), and Zihui Zhang(张紫辉). A polarization mismatched p-GaN/p-Al0.25Ga0.75N/p-GaN structure to improve the hole injection for GaN based micro-LED with secondary etched mesa[J]. 中国物理B, 2023, 32(1): 18509-018509. |

| [7] | Xiaoyu Liu(刘晓宇), Yong Zhang(张勇), Haoran Wang(王皓冉), Haomiao Wei(魏浩淼),Jingtao Zhou(周静涛), Zhi Jin(金智), Yuehang Xu(徐跃杭), and Bo Yan(延波). High frequency doubling efficiency THz GaAs Schottky barrier diode based on inverted trapezoidal epitaxial cross-section structure[J]. 中国物理B, 2023, 32(1): 17305-017305. |

| [8] | Guangbao Lu(陆广宝), Jun Liu(刘俊), Chuanguo Zhang(张传国), Yang Gao(高扬), and Yonggang Li(李永钢). Dynamic modeling of total ionizing dose-induced threshold voltage shifts in MOS devices[J]. 中国物理B, 2023, 32(1): 18506-018506. |

| [9] | Taofei Pu(蒲涛飞), Shuqiang Liu(刘树强), Xiaobo Li(李小波), Ting-Ting Wang(王婷婷), Jiyao Du(都继瑶), Liuan Li(李柳暗), Liang He(何亮), Xinke Liu(刘新科), and Jin-Ping Ao(敖金平). Normally-off AlGaN/GaN heterojunction field-effect transistors with in-situ AlN gate insulator[J]. 中国物理B, 2022, 31(12): 127701-127701. |

| [10] | Zhi-Peng Yin(尹志鹏), Sheng-Sheng Wei(尉升升), Jiao Bai(白娇), Wei-Wei Xie(谢威威), Zhao-Hui Liu(刘兆慧), Fu-Wen Qin(秦福文), and De-Jun Wang(王德君). Ozone oxidation of 4H-SiC and flat-band voltage stability of SiC MOS capacitors[J]. 中国物理B, 2022, 31(11): 117302-117302. |

| [11] | Chenkai Zhu(朱晨凯), Linna Zhao(赵琳娜), Zhuo Yang(杨卓), and Xiaofeng Gu(顾晓峰). Degradation and breakdown behaviors of SGTs under repetitive unclamped inductive switching avalanche stress[J]. 中国物理B, 2022, 31(9): 97303-097303. |

| [12] | Xinxin Zuo(左欣欣), Jiang Lu(陆江), Xiaoli Tian(田晓丽), Yun Bai(白云), Guodong Cheng(成国栋), Hong Chen(陈宏), Yidan Tang(汤益丹), Chengyue Yang(杨成樾), and Xinyu Liu(刘新宇). Improvement on short-circuit ability of SiC super-junction MOSFET with partially widened pillar structure[J]. 中国物理B, 2022, 31(9): 98502-098502. |

| [13] | Pei Shen(沈培), Ying Wang(王颖), and Fei Cao(曹菲). A 4H-SiC trench MOSFET structure with wrap N-type pillar for low oxide field and enhanced switching performance[J]. 中国物理B, 2022, 31(7): 78501-078501. |

| [14] | Yun-Long He(何云龙), Fang Zhang(张方), Kai Liu(刘凯), Yue-Hua Hong(洪悦华), Xue-Feng Zheng(郑雪峰),Chong Wang(王冲), Xiao-Hua Ma(马晓华), and Yue Hao(郝跃). Simulation design of normally-off AlGaN/GaN high-electron-mobility transistors with p-GaN Schottky hybrid gate[J]. 中国物理B, 2022, 31(6): 68501-068501. |

| [15] | Si-De Song(宋思德), Guo-Zhu Liu(刘国柱), Qi He(贺琪), Xiang Gu(顾祥), Gen-Shen Hong(洪根深), and Jian-Wei Wu(吴建伟). Combined effects of cycling endurance and total ionizing dose on floating gate memory cells[J]. 中国物理B, 2022, 31(5): 56107-056107. |

|

||