† Corresponding author. E-mail:

Project supported by the National Key R&D Program of China (Grant No. 2017YFB0404100) and Science and Technology Planning Project of Guangdong Province, China (Grant No. 2017B010112001).

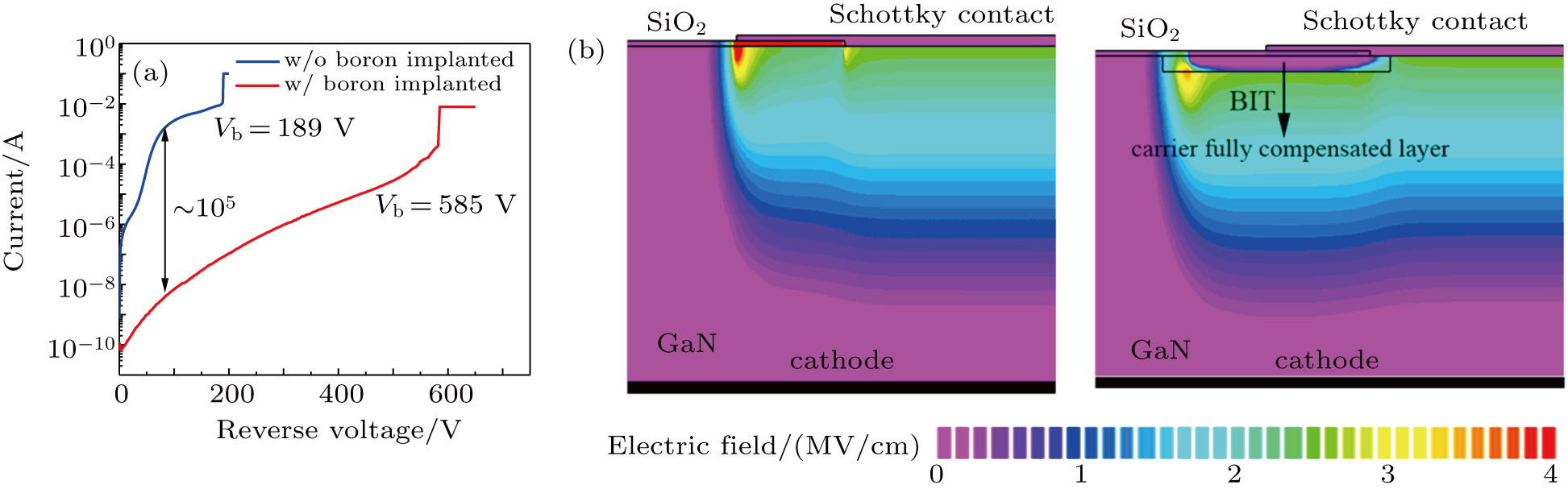

The vertical GaN-on-GaN Schottky barrier diode with boron-implanted termination was fabricated and characterized. Compared with the Schottky barrier diode (SBD) without boron-implanted termination, this SBD effectively improved the breakdown voltage from 189 V to 585 V and significantly reduced the reverse leakage current by 105 times. In addition, a high Ion/Ioff ratio of ∼108 was achieved by the boron-implanted technology. We used Technology Computer Aided Design (TCAD) to analyze reasons for the improved performance of the SBD with boron-implanted termination. The improved performance of diodes may be attributed to that B+ could confine free carriers to suppress electron field crowding at the edge of the diode, which could improve the breakdown voltage and suppress the reverse leakage current.

Wide bandgap materials have received increasing attention in the research and development of power electronic devices for energy conversion.[1–3] Gallium nitride (GaN) is a promising candidate material due to its large bandgap, high electron mobility, and high breakdown electric field.[4,5] In particular, vertical GaN power devices using GaN on GaN substrate materials with a low dislocation density (∼ 106 cm−2) are greatly developed. For example, p–n diodes (PNDs) with breakdown voltage (Vb) over 4 kV[6] and transistors with normally-off operation were well demonstrated.[7,8]

Compared with PNDs, Schottky barrier diodes (SBDs) have low turn-on voltage (Von) and fast switching. Therefore, Schottky barrier diodes have significant applications in the field of high frequency and high power devices.[9] However, SBDs typically suffer from large reverse leakage current due to the Schottky barrier lowering at high reverse biases. To suppress the reverse leakage current, advanced device structures, such as junction barrier Schottky diodes, have been well demonstrated in SiC.[10,11] But this technology is difficult to achieve in vertical GaN devices owing to the great challenge in selective Mg-implantation and activation.[12] Several methods have been used to suppress the edge leakage current and increase Vb in vertical GaN SBDs, especially including field plates with a deep trench[13,14] and a high-resistivity region around the device edge using ion implantation which can create deep-level traps.[15] What is more, introducing ions in the edge termination, which can compensate free carriers, is a common method to increase the performance of the vertical GaN power devices.[16]

There already have been a lot of reports on SiC power devices with boron-implanted technology, such as boron-implanted edge termination for 4H-SiC Schottky rectifiers and boron related deep centers caused by ions implantation in 6H-SiC.[17–19] Moreover, there have been some reports about GaN vertical-cavity surface-emitting diodes and GaN MOSFETs with boron ions implantation technology.[20–22] However, there are few reports about vertical GaN-on-GaN SBDs with boron-implanted technology.

In this work, we fabricated a vertical GaN-on-GaN SBD with the B+-implanted termination (BIT). Diodes with and without the BIT were characterized. The diode without the BIT is broken down at 189 V, its Schottky barrier height is 0.68 eV and its Ion/Ioff ratio is ∼ 105. Compared with the GaN SBD without B+ implanted termination technology, this SBD with the BIT has 105 × reverse leakage reduction and enhances the breakdown voltage up to ∼ 585 V. Furthermore, the SBD with the BIT obtains a high Ion/Ioff ratio of 108 and the Schottky barrier height (SBH) of 0.82 eV. This improved performance of the diode may be attributed to that B+ could confine free carriers at the edge of the diode.[20,21]

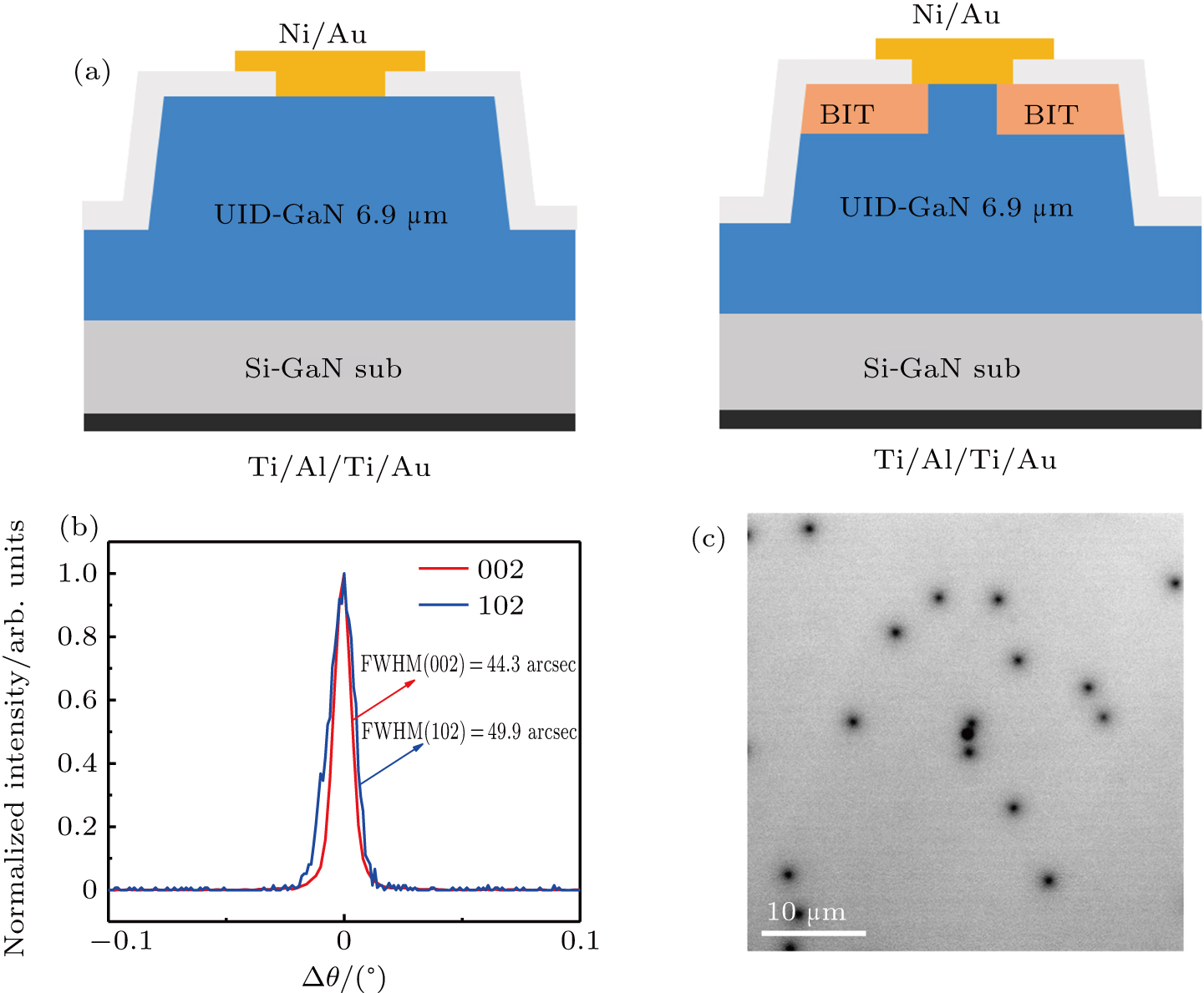

Vertical GaN SBDs were fabricated on bulk GaN substrate materials. Figure

| Fig. 1. (a) The schematic structures of the vertical GaN-on-GaN SBDs with and without the BIT. (b) Rocking curves of the (002) and (102) planes of the GaN epilayer. (c) The plane-section CL image. |

| Fig. 2. (a) The concentration of C, H, O, and Si in GaN-on-GaN MOCVD growths by SIMS. (b) The AFM image of the epilayer in a range of 10 μm × 10 μm. |

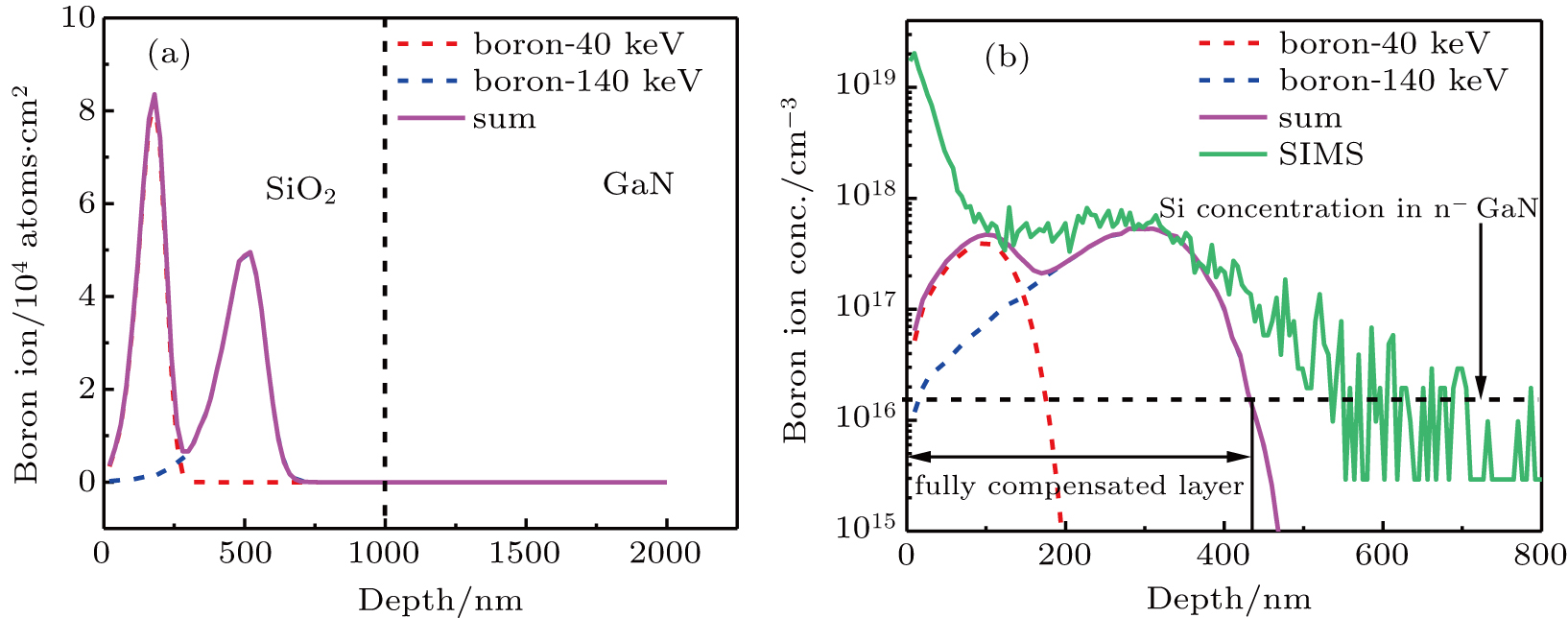

The device fabrication started with 1-μm deep mesa isolation etch by inductively coupled plasma (ICP). Then 1-μm thick SiO2 was deposited by plasma-enhanced chemical vapor deposition (PECVD), followed by selectively etching of SiO2 to form a hard mask for the next ion implantation. As shown in Fig.

Figure

| Fig. 4. (a) The C–V characteristic of the device drift layer. (b) The extracted free carrier concentration in the device drift layer. |

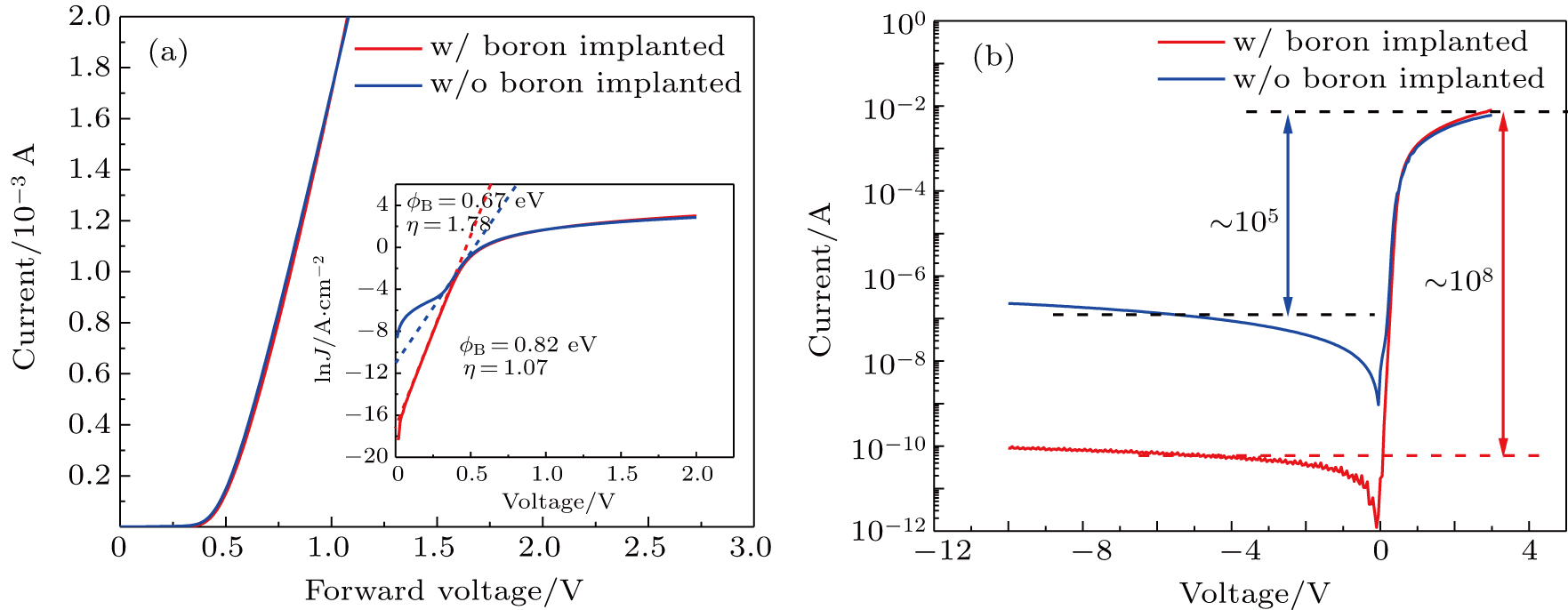

Figure

| Fig. 5. (a) Forward characteristics of the diodes with and without the BIT. Inset: ln(J) as a function of V. (b) The I–V characteristics of the diodes with and without the BIT. |

Table

| Table 1. Comparison of forward characteristics of the diodes with and without the BIT. . |

Figure

| Fig. 6. (a) Reverse I–V characteristics of the diodes with and without the BIT. (b) Simulated electric field distributions in the diodes without the BIT (left) and with the BIT (right) at −600 V. |

The above results show that the B+-implanted termination technology could improve the performance of vertical GaN-on-GaN SBDs such as breakdown voltage and reverse leakage current. The reason why the BIT structure could improve the performance of the diodes is that B+ could confine free carriers in the GaN drift layer. As shown in Fig.

We fabricated and characterized vertical GaN-on-GaN Schottky barrier diodes with and without boron-implanted termination. The Schottky barrier height in the diode with the BIT was 0.82 eV and the ideality factor was 1.07. Compared to the diode without the BIT, the breakdown voltage was improved from 189 V to 585 V, the Ion/Ioff ratio was in the order of 108, and the reverse leakage current was reduced by five orders of magnitude. The condition parameters of B+ implantation were simulated by SRIM. And we attributed the improved performance of the diode with the BIT to boron ion confining free carriers at the edge of the diode. From TCAD simulation results, the electric field crowding effect at the boundary of the diode with the BIT was suppressed, which could improve the breakdown voltage and suppress the reverse leakage current. Therefore, the boron ions implantation technology shows great potential for vertical GaN-on-GaN power devices as the termination structure.

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] | |

| [20] | |

| [21] | |

| [22] | |

| [23] | |

| [24] | |

| [25] | |

| [26] | |

| [27] | |

| [28] | |

| [29] | |

| [30] |