† Corresponding author. E-mail:

Project supported by the National Natural Science Foundation of China (Grant Nos. 61334002, 61106106, and 61474091), the New Experiment Development Funds for Xidian University, China (Grant No. SY1434), and the Scientific Research Foundation for the Returned Overseas Chinese Scholars, State Education Ministry, China (Grant No. JY0600132501).

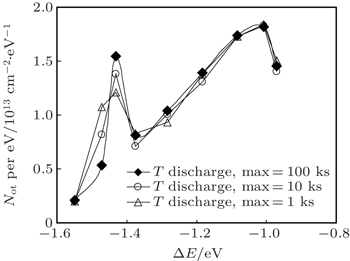

In this paper, the principle of discharge-based pulsed I–V technique is introduced. By using it, the energy and spatial distributions of electron traps within the 4-nm HfO2 layer have been extracted. Two peaks are observed, which are located at ΔE ∼ −1.0 eV and −1.43 eV, respectively. It is found that the former one is close to the SiO2/HfO2 interface and the latter one is close to the gate electrode. It is also observed that the maximum discharge time has little effect on the energy distribution. Finally, the impact of electrical stress on the HfO2 layer is also studied. During stress, no new electron traps and interface states are generated. Meanwhile, the electrical stress also has no impact on the energy and spatial distribution of as-grown traps. The results provide valuable information for theoretical modeling establishment, material assessment, and reliability improvement for advanced semiconductor devices.

In order to realize the aggressively continuous downscaling of CMOS technology, high-k materials are important approaches. With the aid of high-k materials, a small equivalent oxide thickness (EOT) can be realized even under a thick physical thickness, which can decrease the static power dissipation in integrated circuits and improve the data retention in Flash memory.[1–3] Meanwhile, high-k materials are also used in III–V high electron mobility transistors (HEMTs) to replace the conventional Schottky gate. By utilizing it, the gate leakage current can be decreased, which can improve the breakdown voltage, power added efficiency, and long-term reliability.[4,5] Nowadays, high-k materials are becoming more and more important in semiconductor devices.

Besides the regular Al2O3 dielectric, HfO2 is also considered as a good high-k material due to the relatively high dielectric constant, good thermal stability, etc.[6] Generally, the quality of high-k is not so good as that of mature SiOxNy dielectric. Previous works have demonstrated that there are large densities of pre-existing traps in HfO2,[7,8] which are a few orders of magnitude higher than that in SiO2. It has become a bottleneck that hinders the wide application of high-k materials and improvement of long-term reliability. Therefore, in-depth understanding on the properties of traps in HfO2 becomes an important issue. Among it, the energy and spatial distribution of electron traps within HfO2 is a major concern, which plays a vital role in theoretical modeling establishment and material assessment. Early works on trap distribution study were mainly based on the numerical calculation.[9,10] However, direct experimental evidence is still rather limited.

There are two obstacles that limit the in-depth experimental study on electron traps in HfO2. Firstly, the trapped electron in HfO2 can be easily discharged. Conventional C–V/I–V techniques, which feature the measurement speed of 10 s, are too slow to correctly measure the defects due to the fast discharging in HfO2. Secondly, the existing characterization techniques for electron trap energy distribution have obvious limitations. For example, the advanced charge-pumping technique can only detect the electron traps which are at about 1 nm in the high-k layer, due to the minimum frequency being limited at around 100 Hz.[2,11] The charge injection and sensing (CIS) technique can detect the traps at about 2–3 nm within the high-k layer. This region, however, is still very limited in comparison with the entire high-k layer.[12] Then most of the electron traps within the high-k layer can still not be detected. To overcome it, we developed a discharge-based multi-pulse technique,[13,14] and the electron trap energy distribution within HfO2 has been discussed. However, the spatial distribution has not been discussed. Furthermore, the impact of electrical stress on electron traps has not been explored.

In this work, the principle of our developed discharge-based pulsed I–V technique will be briefly introduced. With the aid of it, the energy and spatial distributions of electron traps within the HfO2 layer have been extracted. The effect of discharge time on the electron trap distribution is also discussed. Furthermore, the influence of electrical stress on electron traps within HfO2 and interface states at the substrate/gate dielectric are investigated as well. The above works provide valuable information for theoretical modeling estimation, material and processing assessment, and reliability improvement in advanced semiconductor devices.

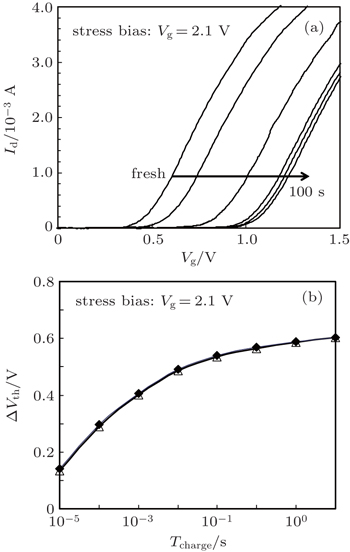

The devices used in this paper are nMOSFETs that are fabricated on p-type Si wafer. The gate dielectric consists of 1-nm SiO2 and 4-nm HfO2, which is deposited by atomic layer deposition. The detailed process information can be found in Ref. [13]. By using the HP 4156B semiconductor parameter analyzer, the conventional DC Id−Vg curve of the nMOSFET is shown in Fig.

| Fig. 1. The Id–Vg curves measured by the DC I–V technique and pulsed I–V technique before and after stress on a fresh device, respectively. The stress is 2.1 V for 10 s. |

It is known that fast detrapping exists in MOSFETs with HfO2 gate dielectric. In this paper, a pulsed I–V technique is used to measure the transfer characteristics (Id–Vg) of devices.[15] It can significantly shorten the measurement period, and improve the measurement accuracy accordingly. The pulse measurement system consists of a pulse generator, oscilloscope and current–voltage amplifier,[15] which can obtain the transfer characteristics within 5 μs in this paper. For the conventional DC I–V technique, it is about 10 s. The Id–Vg curves measured by pulsed technique on the identical fresh device are also presented in Fig.

Furthermore, the effect of the measurement technique was also studied in this paper. A stress of 2.1 V for 10 s was applied on a fresh device. After the stress, the conventional DC I–V and pulsed I–V were carried out immediately to obtain the Id–Vg curves. As shown in Fig.

Considering the above advantages, the pulsed I–V technique becomes very important for accurate characterization of the trapping and detrapping in a device with HfO2 gate dielectric. In this paper, the effective trap density can be obtained by the shift of threshold voltage, ΔVth. For data process simplicity, the threshold voltage is extracted from the Id–Vg curve at a constant drain current of 10−4 A with a drain bias of 100 mV.

To probe the electron trap energy distribution, we developed a discharge-based pulsed I–V technique. The principle will be introduced briefly as follows.

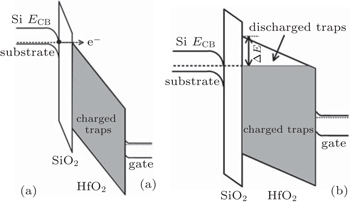

Firstly, the entire electron traps within the HfO2 layer will be charged by applying a high positive bias on the gate. As shown in Fig.

| Fig. 2. The schematic energy band diagrams of nMOSFET with SiO2/HfO2 gate dielectric for (a) charging at high positive gate bias and (b) discharging at lower gate bias, respectively. |

During the above process, the following respects should be noted: (I) pulsed I–V is used to monitor the Vth at the pre-set time, which is to ensure that the discharge is saturated; (II) during discharge, the discharge time should be long enough to ensure that all electron traps are discharged; (III) the gate bias for charge or discharge should be safe, i.e., new electron traps or interface states should not be generated during these processes; (IV) the time interval between the two consecutive process, such as charge and discharge, should be minimized to zero to avoid the undesired detrapping. With the aid of a pulse generator, it can be easily realized. However, it cannot be easily realized in a conventional DC measurement system; (V) ΔE, as shown in Fig.

In this paper, the gate bias for filling the empty electron traps is selected as Vg = 2.1 V, which is high enough to fill the electron traps with a shallow energy level in the HfO2 layer. Figure

After the filling, the gate bias is immediately switched to a series of lower gate bias sequentially for discharging. Figure

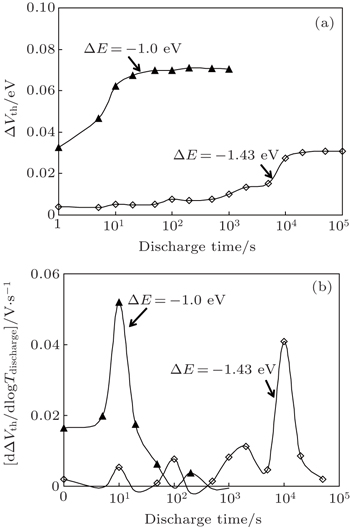

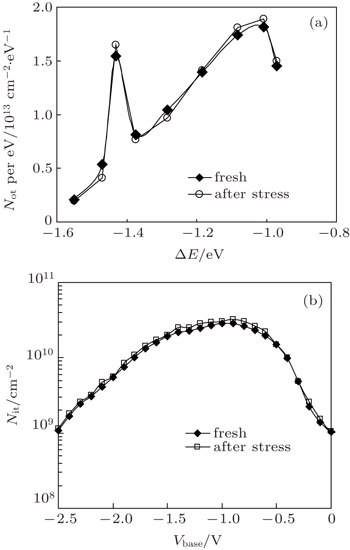

It should be noted that the maximum discharge time used above is 100 ks. Although it can improve the accuracy of characterization, however, it is very time-consuming. In order to investigate the effect of discharge time on electron trap energy distribution, the maximum discharge time is decreased to 10 ks and 1 ks, respectively. The energy distribution results are presented in Fig.

| Fig. 5. The trap density per electronvolt versus ΔE with different discharge time. The maximum discharge times are 100 ks, 10 ks and 1 ks, respectively. The charge bias is 2.1 V for 10 s. |

Besides the energy distribution, the spatial distribution of electron traps within HfO2 is also eagerly required during theoretical modeling, etc. Generally, the calculation for spatial distribution is very complex. According to the tunneling theory, a longer discharge time corresponds to discharge traps farther away from the substrate. Figure

Note that the above investigations are focused on the as-grown electron traps in HfO2. To the best of our knowledge, little study has been paid on the newly generated electron traps under electrical stress. In order to investigate it, a high positive bias of 3.0 V for 100 s is applied on the gate of the device. Following the stress, the discharge-based pulsed technique is carried out. Figure

In this paper, the energy and spatial distributions of electron traps within the 4-nm HfO2 layer have been investigated. By using the discharge-based pulsed I–V technique, it is found that there are two peaks existing in HfO2, which are located at ΔE ∼ −1.0 eV and −1.43 eV, respectively. The former one is close to the SiO2/HfO2 interface, however, the latter one is close to the gate electrode. Finally, the effect of electrical stress on the distribution of electron traps has also been studied. During stress, there is no additional electron traps and interface states are newly generated. The stress also has no impact on the as-grown traps.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 | |

| 16 | |

| 17 | |

| 18 | |

| 19 |