† Corresponding author. E-mail:

Project supported in part by the National Key Research and Development Program of China (Grant No. 2016YFB0100601), the National Natural Science Foundation of China (Grant Nos. 61674169 and 61974159), and the Support from a Grant-In-Aid from the Youth Innovation Promotion Association of the Chinese Academy of Sciences.

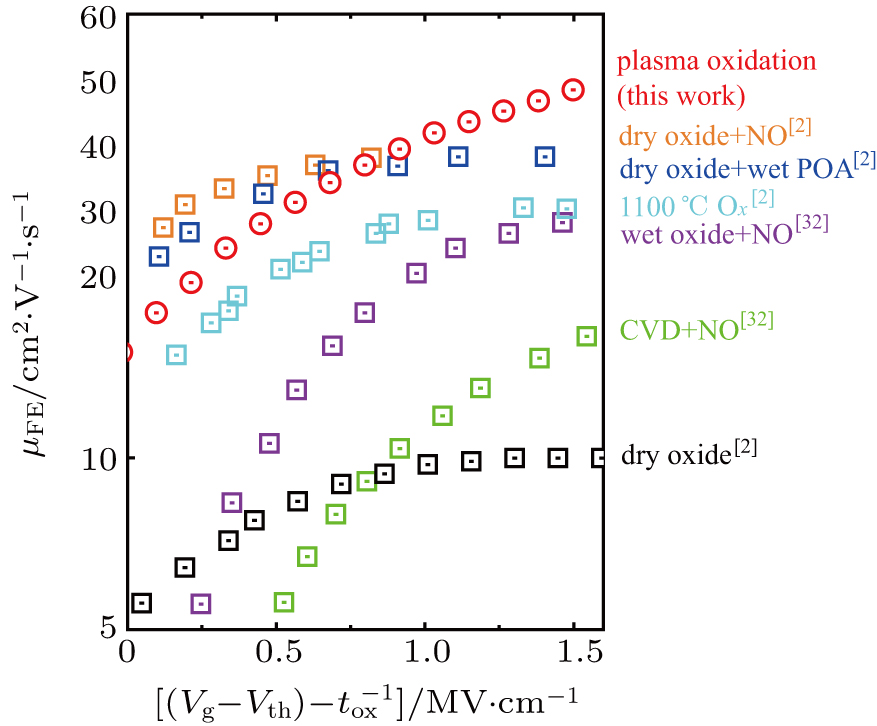

The microwave plasma oxidation under the relatively high pressure (6 kPa) region is introduced into the fabrication process of SiO2/4H-SiC stack. By controlling the oxidation pressure, species, and temperature, the record low density of interface traps (∼ 4 × 1010 cm−2⋅eV−1@Ec − 0.2 eV) is demonstrated on SiO2/SiC stack formed by microwave plasma oxidation. And high quality SiO2 with very flat interface (0.27-nm root-mean-square roughness) is obtained. High performance SiC metal–oxide–semiconductor field-effect transistors (MOSFETs) with peak field effect mobility of 44 cm−2 ⋅eV−1 is realized without additional treatment. These results show the potential of a high-pressure plasma oxidation step for improving the channel mobility in SiC MOSFETs.

SiC metal–oxide–semiconductor field-effect transistors (MOSFETs) are the promising devices for applications in areas where high power, high temperature, and high speeds are desired.[1] However, one of the technological concerns that affect the behavior of 4H-SiC MOSFETs is the low inversion channel mobility. In general, the channel mobility less than 10 cm2⋅V−1⋅s−1 is typically obtained by using thermally grown SiO2 layers as gate oxide.[2] This is about two orders of magnitude below the bulk mobility of 4H-SiC, the polytype most commonly investigated for power electronics applications, due to the high density of interface traps (Dit), in the order of 1013 eV−1⋅cm−2, near the conduction band edge. It is attributed to the existence of different types of charge traps either in gate oxide or at the SiO2/SiC interface, such as the dangling bonds, carbon clusters, and near interface traps.[3] Various channel engineering processes have been proposed to address these issues beyond nitrogen-monoxide (NO) annealing,[4–9] the process that is currently most widely used, but rarely leads to mobility above 40 cm2⋅V−1⋅s−1, especially with a heavy p-type doping concentration (> 1017 cm−3).[10–12] This doping level is typical for power double implanted MOSFETs (DMOSFETs).

Plasma oxidation, utilizing a highly activated oxygen plasma, is one of the low temperature techniques used to grow dielectric films on semiconductor surfaces. The study of SiC oxidation by plasma began around 1997 and Lucovsky et al. reported that SiC can be oxidized by remote plasma-assisted oxidation.[13] Recently, Kim et al. investigated that interface traps generation in the SiO2 oxide is more suppressed in the high-power plasma oxidation process than in the thermal oxidation process.[14,15] Early studies preliminarily revealed the equipment principle of plasma oxidation, mechanism of plasma oxidation, and characteristics of plasma oxide.[16–18] However, the plasma oxidation has not been reported for the fabrication of SiC MOSFET.

In the present article, for the first time, high-pressure microwave plasma oxidation process has been introduced for SiC MOSFETs fabrication. We have systematically studied the material and electrical characteristics of the plasma oxide layer. And the MOSFETs with a heavy p-type doping concentration (∼ 1017 cm−3) were fabricated and the field effect mobility was extracted. The high-pressure plasma SiO2/4H-SiC stack presents a significant improvement of interface properties over those grown by other oxidation methods.

A schematic diagram of the microwave oxidation equipment used in our work is shown in Fig.

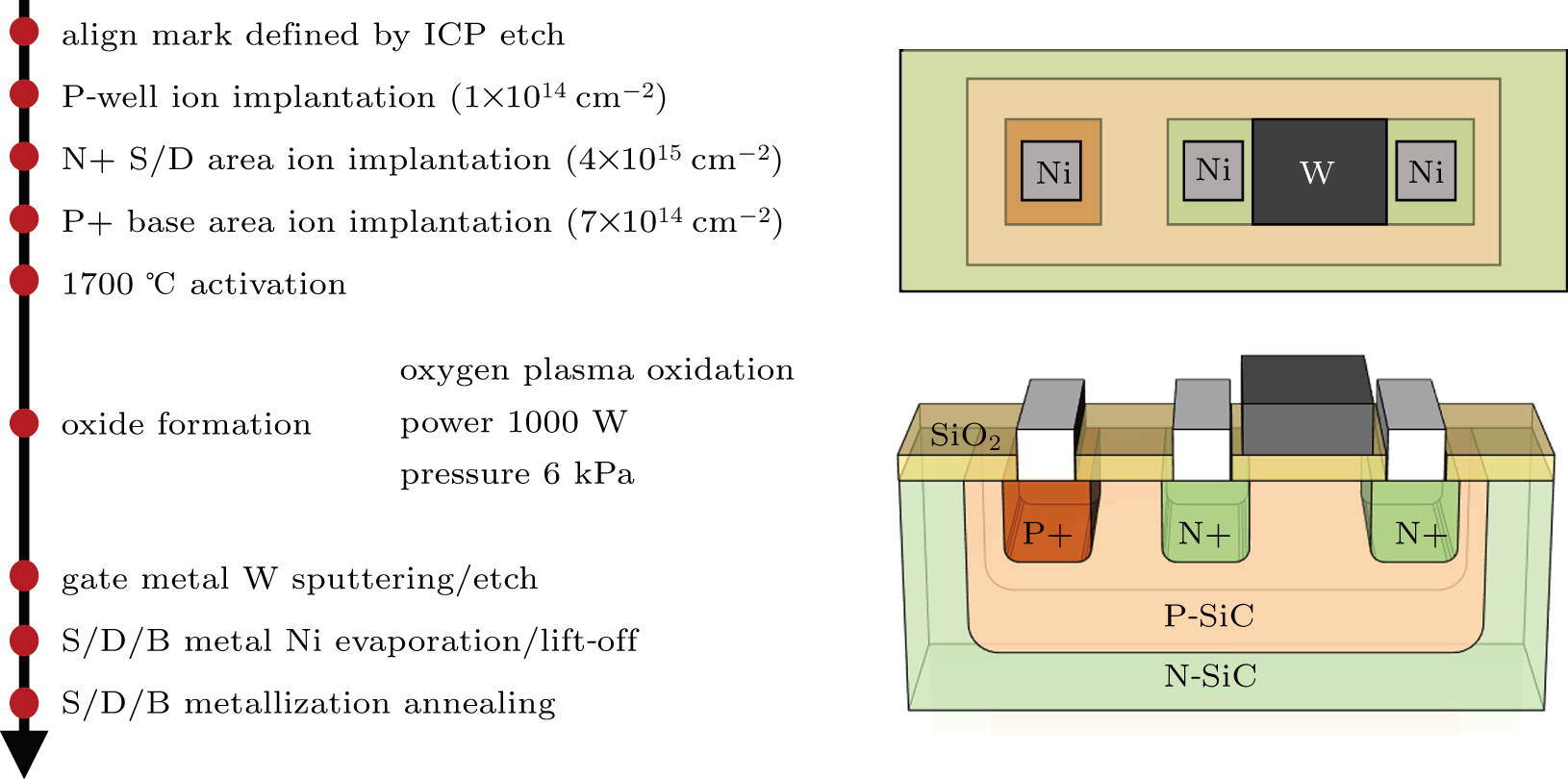

All devices were fabricated on the N-type epitaxial layer (dopant density ≈ 1 × 1016 cm−3) deposited on the (0001) Si-face of 4H-SiC wafers. The fabrication process of metal–oxide–semiconductor (MOS) capacitors is as follows. 4H-SiC wafers were precleaned by using deionized water, acetone, and HF aqueous solution. Then the plasma oxide was grown in the microwave chamber at room temperature and pressure of 6 kPa under a flow of purity (7N) O2 gas and an optimized microwave power of 1000 W.[19] Al electrodes were deposited to form gate (diameter is about 200 μm for capacitance–voltage (C–V) measurement; thickness ≈ 400 nm) and backside Ohmic contacts. The fabrication process of MOSFET is shown in Fig.

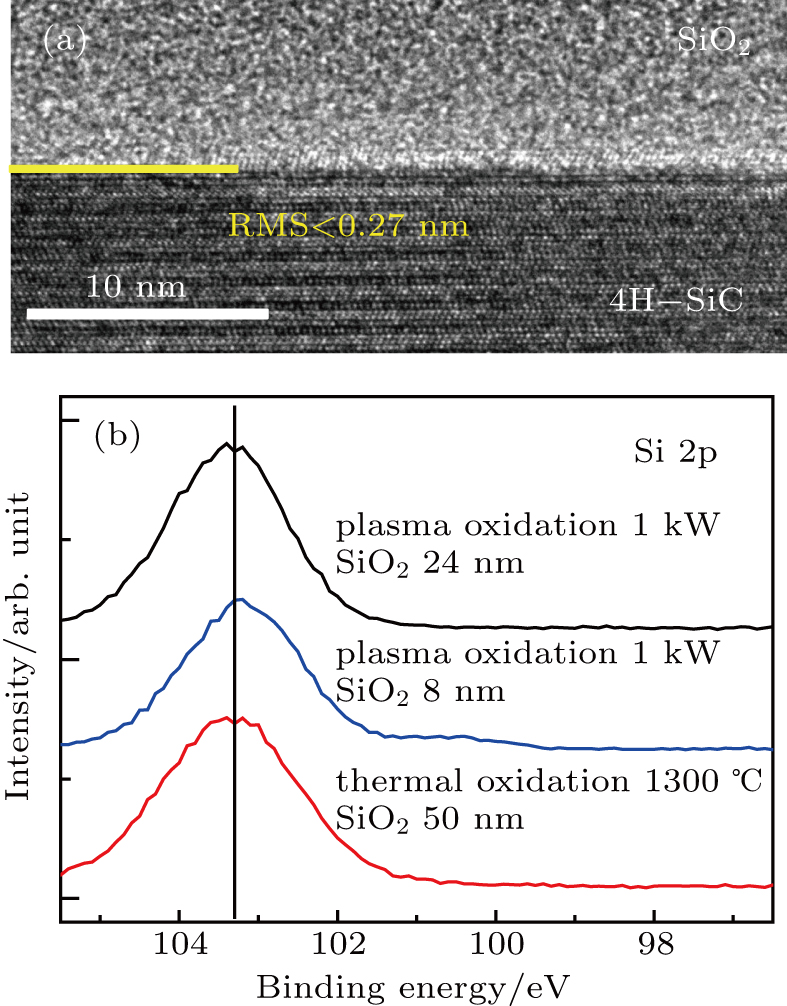

The direct characterization of the SiO2/4H-SiC interface was measured by the transmission electron microscope (TEM). The high resolution TEM images were obtained using a field-emission gun at an acceleration voltage of 200 keV. The chemical bonding states of the SiO2 films grown on the 4H-SiC substrates were examined via high-resolution x-ray photoelectron spectroscopy (XPS); a monochromatic Al x-ray source (hν = 1486.7 eV) with a pass energy of 55 eV and a resolution energy of 0.1 eV was used. Si-2p, C-1s, O-1s, and N-1s spectra were recorded. Binding energies (BE) was corrected for charging effects assuming the BE of the contaminant C-1s peak as lying at 284.6 eV. The interface roughness of the samples was measured via the atomic force microscopy (AFM). Before testing, the oxide of all samples was completely removed by using buffer oxide etch (BOE) solution for 60 minutes. Then the morphology of SiO2/4H-SiC interface was examined with testing area of 1 μm × 1 μm. The AFM (XE-200, Park Systems) was used for the surface measurement. Park Systems AFM XEI software programming was used to evaluate the root-mean-square roughness (RMS roughness).

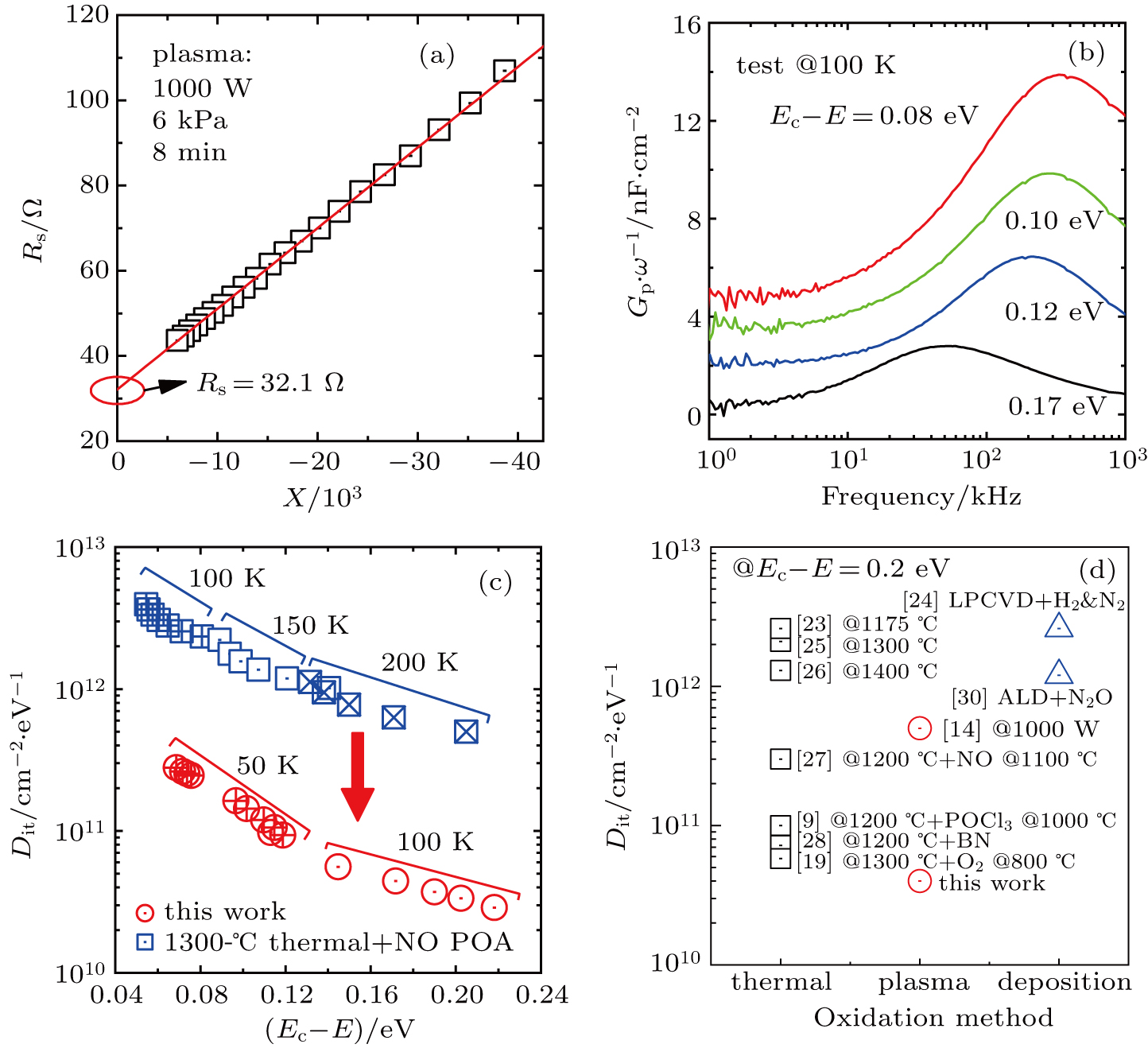

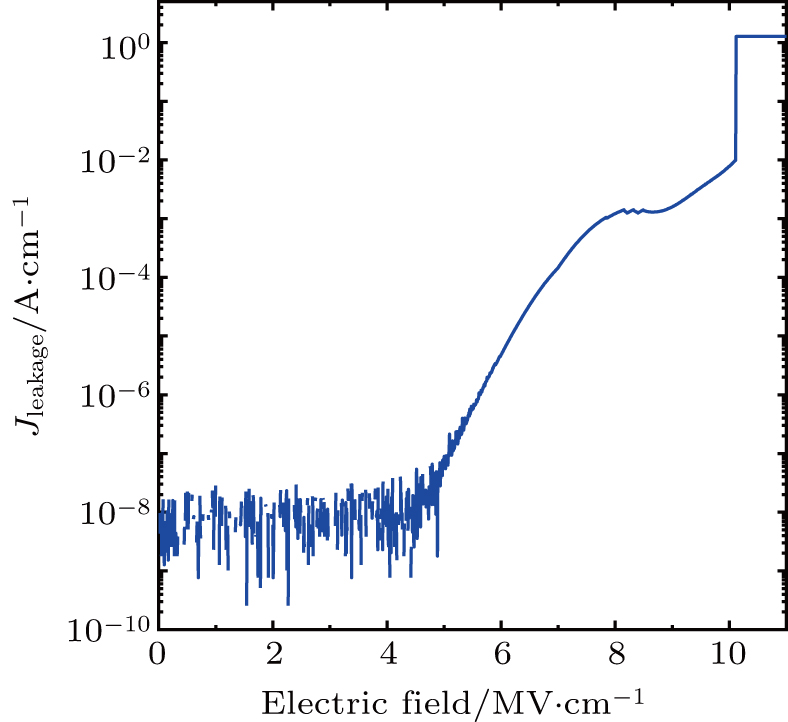

In order to further evaluate the quality of the oxide and the interface formed by the plasma oxidation, the MOS capacitances and MOSFETs were analyzed by the electrical measurements. The capacitance–voltage (C–V) measurement was performed with an Agilent E4990A LCR meter. The density of interface traps (Dit) values were estimated by the conductance method at various temperatures.[20,21] The MOSFET DC characteristics were measured with an Agilent B1500 A semiconductor parameter analyzer. Drain current (Id) as a function of gate voltage (Vg) (Id–Vg) for the MOSFET was measured. The data were collected with the drain voltage (Vd) held at a constant 50-mV bias. And the Id as a function of Vd (Id–Vd) was also measured with the Vg ranging from 2 V to 8 V.

Figure

Figure

The Dit values were determined via calculations by using a combination of forward bias capacitance–frequency (C–f) and conductance–frequency (G–f) measurements to obtain the parallel conductance (Gp), as shown in Fig.

Figure

A high-pressure plasma oxidation process has been demonstrated on 4H-SiC yielding a lower Dit than numerous literature reports of thermal oxides. Field effect mobilities of ∼ 44 cm2⋅V−1⋅s−1 have been extracted from lateral channel MOSFETs with a heavy p-type doping concentration (∼ 1017 cm−3). This is higher than other reports of mobility in 4H-SiC MOSFETs with thermally grown oxides. The enhanced mobility is most likely due to a reduction in trapped charge. The findings in this work demonstrate that a high-pressure plasma oxidation step may be a promising process for improving the channel mobility in SiC MOSFETs.

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] | |

| [20] | |

| [21] | |

| [22] | |

| [23] | |

| [24] | |

| [25] | |

| [26] | |

| [27] | |

| [28] | |

| [29] | |

| [30] | |

| [31] | |

| [32] | |

| [33] | |

| [34] | |

| [35] |