† Corresponding author. E-mail:

In this study, we present an organic field-effect transistor floating-gate memory using polysilicon (poly-Si) as a charge trapping layer. The memory device is fabricated on a N+–Si/SiO2 substrate. Poly-Si, polymethylmethacrylate, and pentacene are used as a floating-gate layer, tunneling layer, and active layer, respectively. The device shows bidirectional storage characteristics under the action of programming/erasing (P/E) operation due to the supplied electrons and holes in the channel and the bidirectional charge trapping characteristic of the poly-Si floating-gate. The carrier mobility and switching current ratio (Ion/Ioff ratio) of the device with a tunneling layer thickness of 85 nm are

Organic memory devices have attracted widespread attention in recent years due to their low cost, light weight, solution processability, and mechanical flexibility characteristics.[1–3] The different material systems and working mechanisms used in organic memory devices can be classified into three different configurations, namely, capacitor-type,[4] resistor-type,[5] and transistor-type memories.[6] Among these memory devices, transistor-type organic field-effect transistor memory (OFETM) devices have many advantages, such as single-transistor realization,[7] nondestructive readout,[8] multi-bit storage,[9,10] and compatibility with CMOS technology. OFETM devices have a structure similar to that of an organic field-effect transistor (OFET), except for a supplementary charge trapping layer that is inserted into the gate dielectric.[11] Considerable efforts have been made to enhance the performance of OFET floating-gate memory (OFET-FGM) devices. One effective method is to use different conductive or semi-conductive nanoparticles or nanofilms as floating-gates. For example, Au, Ag, Cu, and Pt metal nanoparticles are used as nano-floating-gates to increase the memory window and retention time because trap levels and trap sites can be precisely controlled by the nanoparticles’ species, size, and density.[12–15] Carbon-based nanoparticles include graphene quantum dots,[16] which are a promising alternative to traditional semiconductors due to their easy solution processing techniques and excellent physical and chemical properties; reduced graphene oxide;[17] single-walled carbon nanotubes; and[2] C60.[18] Other floating-gate materials include transition metal dichalcogenides (MoS2),[19] electret materials,[20] and hybrid nanostructures.[21,22] However, the preparation of rare metal nanoparticles is expensive and this process is prone to agglomeration. Two-dimensional (2D) materials are difficult to peel and can easily be contaminated during transfer. As a charge trapping material, polysilicon (poly-Si) has widely been used in inorganic memory devices.[23] However, its application in organic memory has rarely been reported. In the current study, we developed and characterized a nanostructured OFET-FGM device with poly-Si as a floating-gate. The relevant results show that poly-Si exhibits excellent charge capture characteristics in organic memory devices.

The materials and surface morphology of the tunneling layer have a huge influence on the performance of OFET-FGM. The use of different organic materials as a tunneling layer can effectively improve the programming/erasing (P/E) voltage, memory window, and storage switching current ratio of the devices.[24,25] In this experiment, polymethylmethacrylate (PMMA) is used as the tunneling layer of OFET-FGM, the performance of the device is improved by optimizing the tunneling layer thickness, and the typical thickness of the OFET-FGM device is 85 nm.

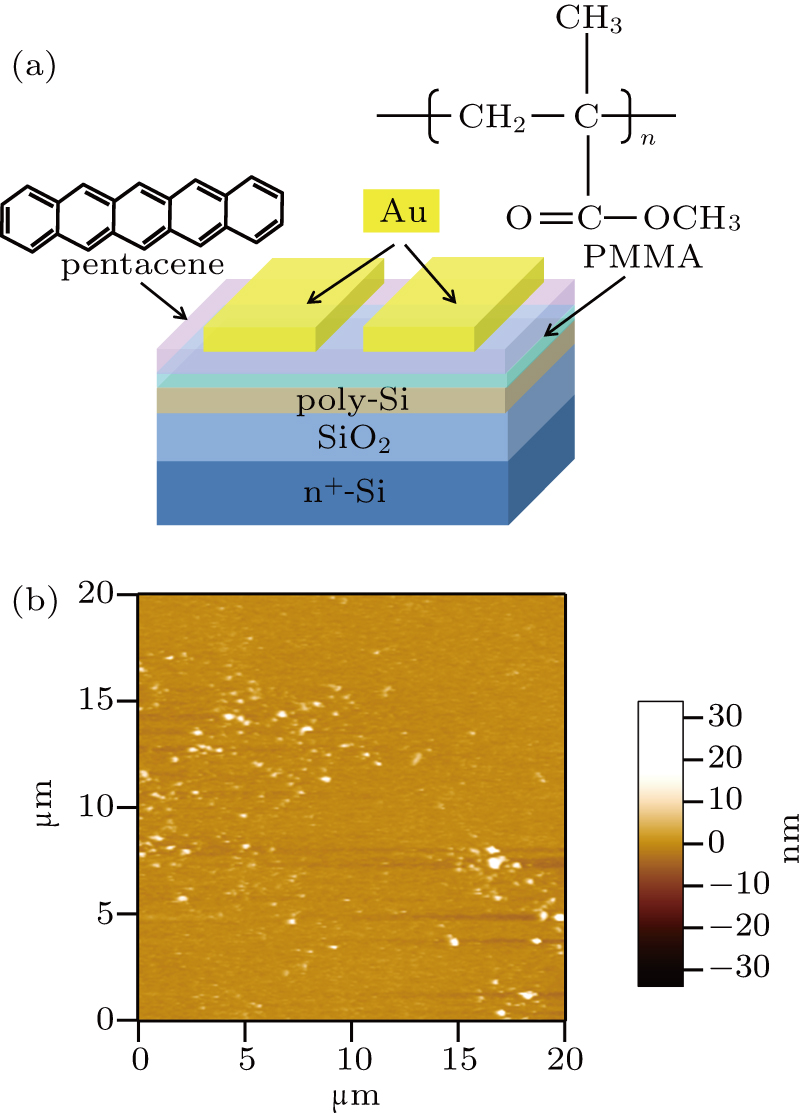

The schematic stereoscopic structure of the OFET-FGM device is shown in Fig.

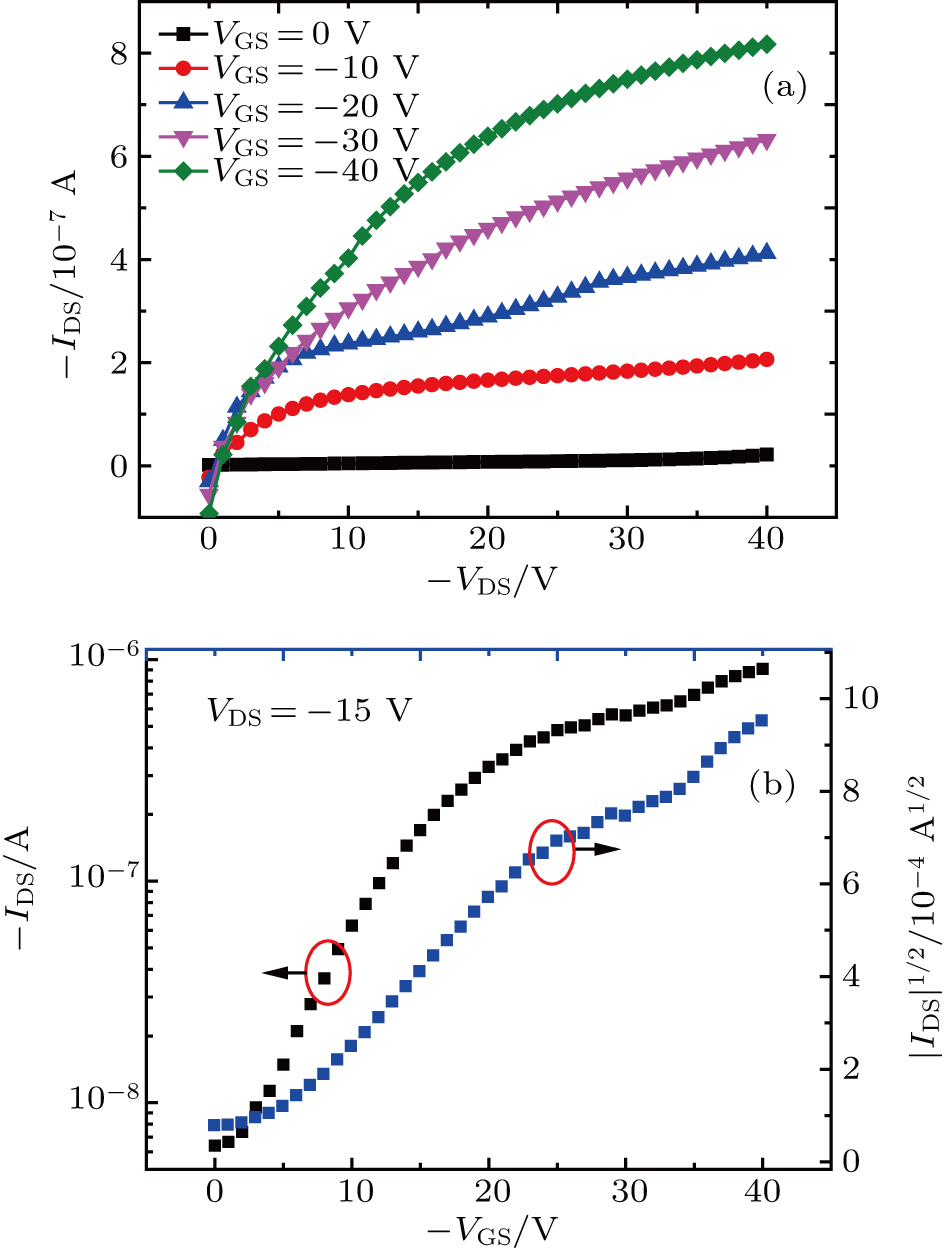

The output characteristics of the OFET-FGM are shown in Fig.

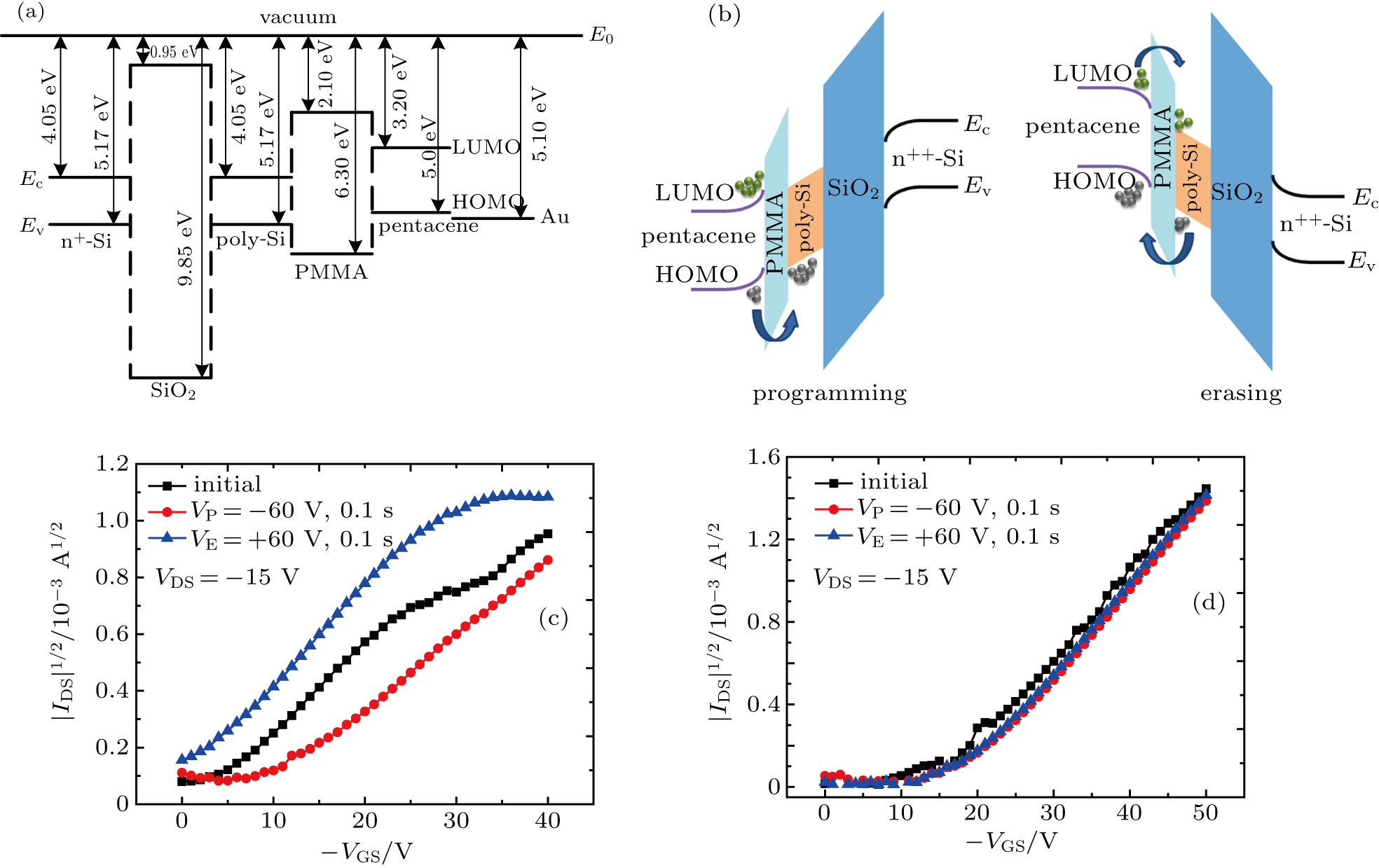

The energy level of the present OFET-FGM is shown in Fig.

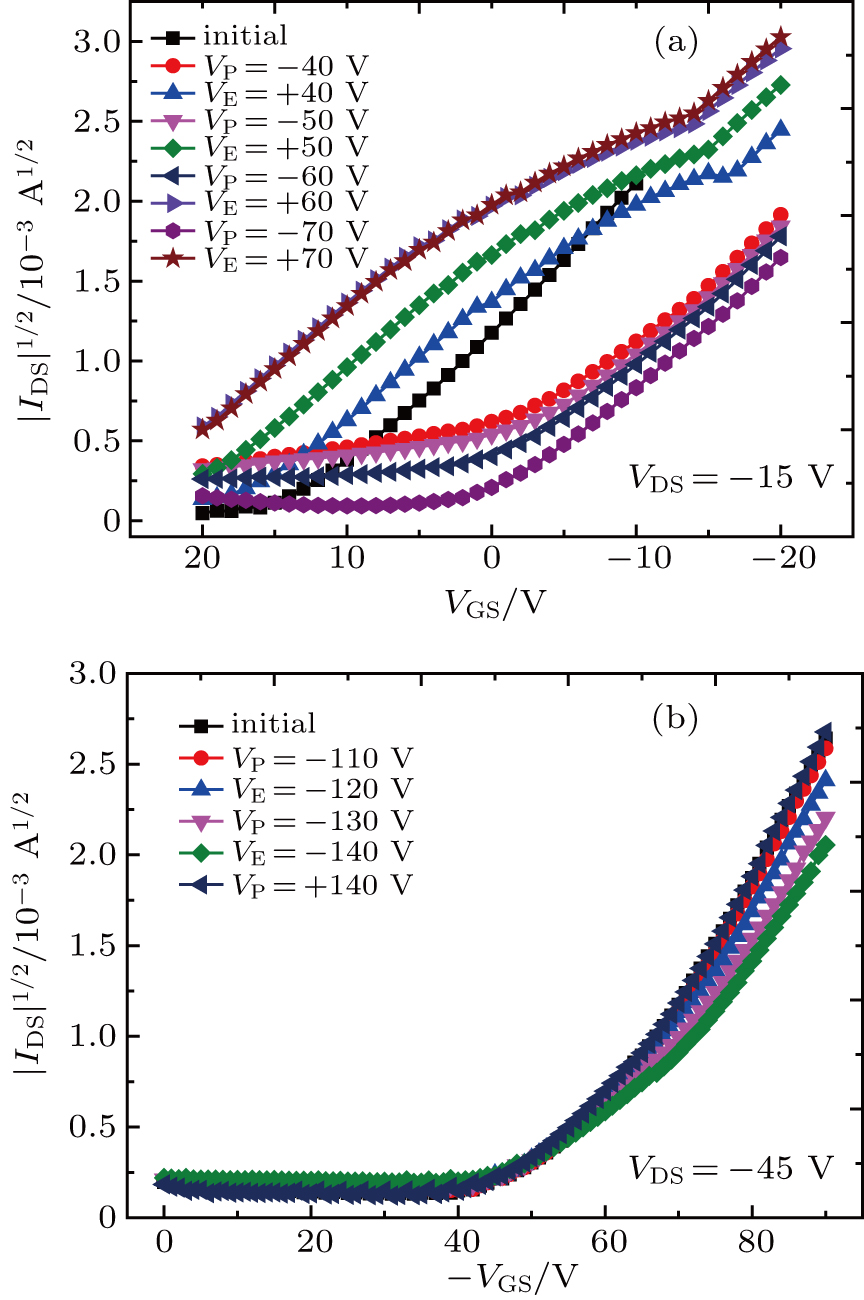

Figure

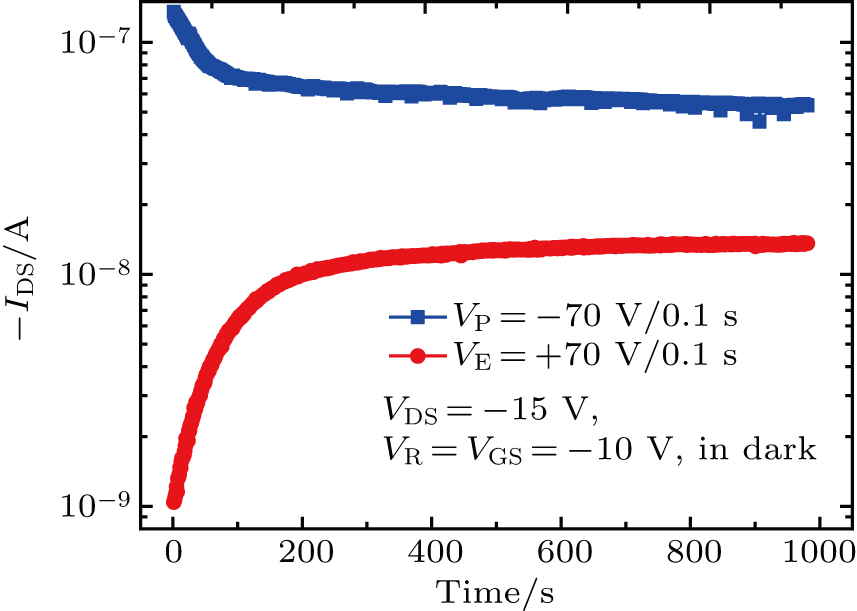

Compared with the initial transfer characteristic curve, the change ratio of VT to VE is higher than that of VT to VP. This finding indicates that the number of electrons injected into the floating-gate during E operation is larger than the number of holes during P operation. This condition indicates that E operations can more easily occur than P operations under certain conditions, and that this phenomenon can be reasonably explained by the hot-carrier injection mechanism. As shown in Fig.

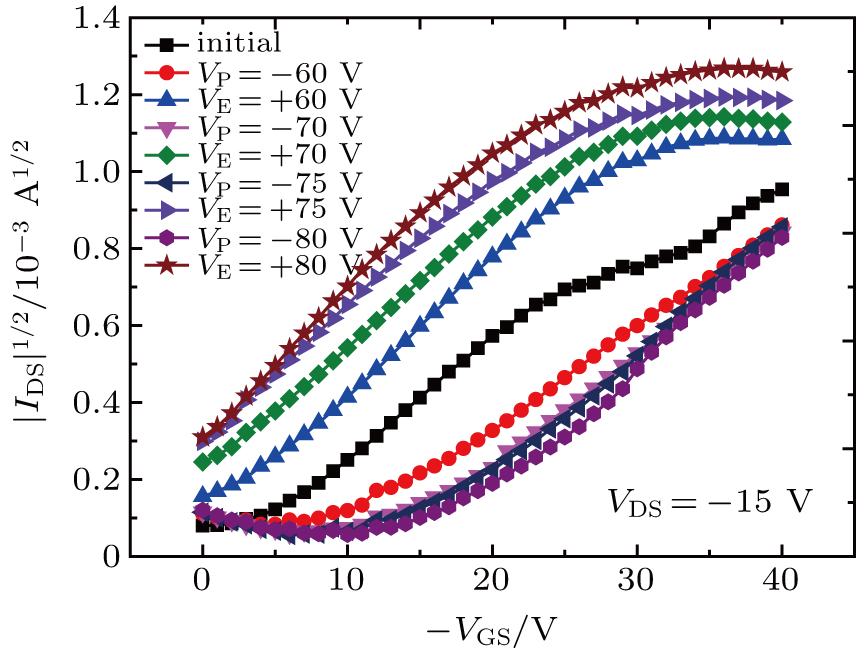

The tunneling layer thickness affects the P/E voltage and retention time of the memory. Figure

Figure

In this work, we present an OFET-FGM with poly-Si as a floating-gate layer. This device exhibits excellent storage characteristics during P/E operation. The storage window varies in the range of 9.28 V–25 V, depending on the magnitude of the P/E pulse voltage. The P/E characteristics indicate that the poly-Si floating-gate is capable of capturing electrons and holes. The required P/E pulse voltage and retention time can be effectively adjusted by changing the tunneling layer thickness. The typical thickness of the tunneling layer is 85 nm, and the optimized OFET-FGM device has relatively low programming voltage and long retention time.

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] | |

| [20] | |

| [21] | |

| [22] | |

| [23] | |

| [24] | |

| [25] | |

| [26] | |

| [27] | |

| [28] |