† Corresponding author. E-mail:

A tunnel field-effect transistor (TFET) is proposed by combining various advantages together, such as non-uniform gate–oxide layer, hetero-gate-dielectric (HGD), and dual-material control-gate (DMCG) technology. The effects of the length of non-uniform gate–oxide layer and dual-material control-gate on the on-state, off-state, and ambipolar currents are investigated. In addition, radio-frequency performance is studied in terms of gain bandwidth product, cut-off frequency, transit time, and transconductance frequency product. Moreover, the length of non-uniform gate–oxide layer and dual-material control-gate are optimized to improve the on-off current ratio and radio-frequency performances as well as the suppression of ambipolar current. All results demonstrate that the proposed device not only suppresses ambipolar current but also improves radio-frequency performance compared with the conventional DMCG TFET, which makes the proposed device a better application prospect in the advanced integrated circuits.

In order to be better applied to integrated circuits, reduce the cost, and improve the on-state current (Ion) and high-frequency characteristics, the size of device needs to be reduced continuously. However, downscaling of the device leads to the increased power dissipation in electronic circuits because of increased leakage current in the off-state. As far as the traditional metal–oxide–semiconductor field-effect transistor (MOSFET) is concerned, it is very difficult to reduce the supply voltage for the purpose of preventing power from dissipating due to the minimum achievable thermionic emission limit of the subthreshold swing (SS) (SS=60 mV/decade) and large off-state current (Ioff). The appearance of tunnel field-effect transistor (TFET) is consistent with the trend of the continuous downsizing of devices for future ultralow power dissipation integrated circuit applications. The TFET can achieve an SS value less than 60 mV/decade at room temperature due to the fact that the carrier injection of the device from source region to channel region is based on band-to-band tunneling (BTBT).[1] Moreover, the TFET can offer other advantages such as low Ioff when the barrier width at the source-channel junction is very large in the off-state,[2–4] high immunity against short-channel effects (SCEs), and small supply voltage below 0.5 V.[5,6] However, the TFET has some shortcomings such as low Ion, ambipolar current (Iamb), and large Miller capacitance. The Ion should be enhanced and ambipolar behavior and Miller capacitance should be well reduced in order to make TFET a better application prospect in the future integrated circuit. Therefore, researchers should comprehensively carry forward the advantages of TFET and overcome its shortcomings. Up to now, many techniques have been proposed to improve Ion, such as narrow bandgap materials,[7–11] high-k gate dielectric,[12] hetero-junction mechanism,[13,14] and doping-less TFETs,[15] source-side pocket doping,[16] hetero-stacked TFET,[17] heteromaterial gate,[18,19] etc. The Iamb can be reduced by using the dual-material control-gate (DMCG) TFETs,[20] charge plasma-based TFETs with gate engineering,[21,22] gate material workfunction engineering,[23] lightly doped drain,[24] and gate–drain underlap structure.[25,26] Moreover, a hetero-gate-dielectric (HGD) TFET with a high gate–oxide dielectric near the source side and a low gate–oxide dielectric near the drain side can enhance Ion and obtain promising radio frequency performance.[27–29]

The downscaling of gate–oxide layer thickness is an important method to enhance the steep switching characteristics of TFETs. But it also leads to large gate leakage current. Moreover, the thickness of the gate–oxide layer is assumed to be uniform in almost all existing TFET devices. Therefore, it is necessary to study the variation of the TFET characteristics in the case of non-uniform gate–oxide layer thickness. The non-uniform structure is defined as a structure whose gate–oxide thickness is thinner on the source-channel side while larger gate–oxide thickness on the drain-channel side. Recently, a TFET with non-uniform gate–oxide shape and an asymmetric hetero-dielectric engineered dual-material double gate (DG) TFET has been analyzed.[30,31] In the present work, a novel device is proposed by combining various advantages together such as non-uniform gate–oxide shape, HGD and DMCG, and named NDMCG TFET. It is intended that in the proposed device the Iamb value can be reduced, the on-off current ratio can be enhanced, and the radio-frequency (RF) performance can be improved by optimizing the structural parameters of device.

The structure of NDMCG TFET is shown in Fig.

The simulations are performed by using silvaco atlas simulator,[32] and the models such as dynamic nonlocal band-to-band tunneling model, Shockley–Read–Hall model, auger recombination model, bandgap narrowing model, and Fermi statistics model are used in this work. The dynamic nonlocal band-to-band tunneling model is an important model in describing the operating principle of TFET. Using the Kane model,[33] the band-to-band tunneling generation rate is expressed as[34]

|

Figure

| Fig. 2. Comparisons of curves of (a) energy band, (b) carrier concentration, and (c) electric field versus X pointion between NDMCG TFET and DMCG TFET under thermal equilibrium state. |

Figure

This subsection is dedicated to the study of the influence of variation in L2 on Ion and Ioff for NDMCG TFET as depicted in Fig.

| Fig. 4. (a) Ion and Ioff varying with L2 for NDMCG TFET, and (b) Iamb varying with L2 for NDMCG TFET and DMCG TFET. |

Figure

| Fig. 5. (a) Ion and Ioff varying with L1 for NDMCG TFET, and (b) Iamb varying with L1 for NDMCG TFET and DMCG TFET. |

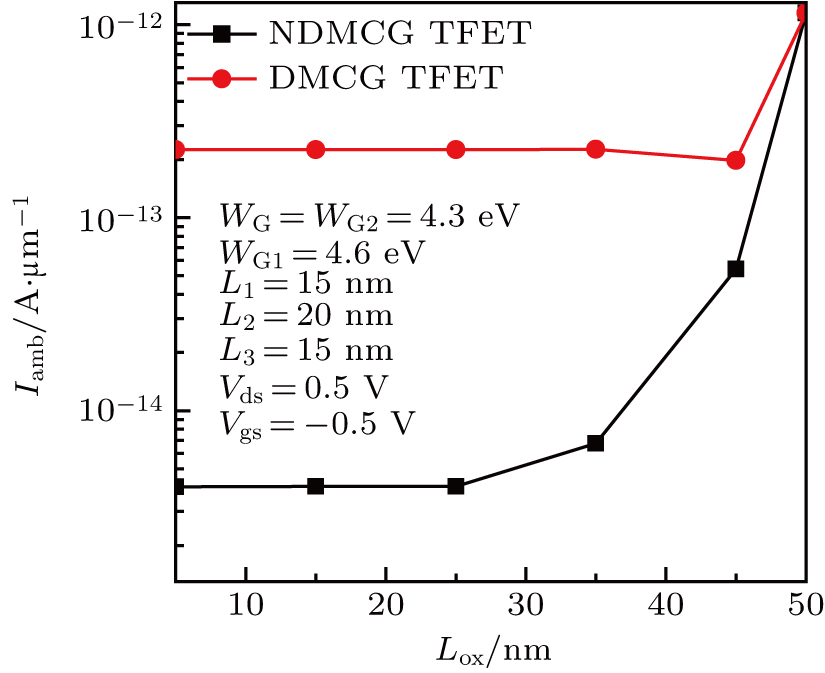

Figure

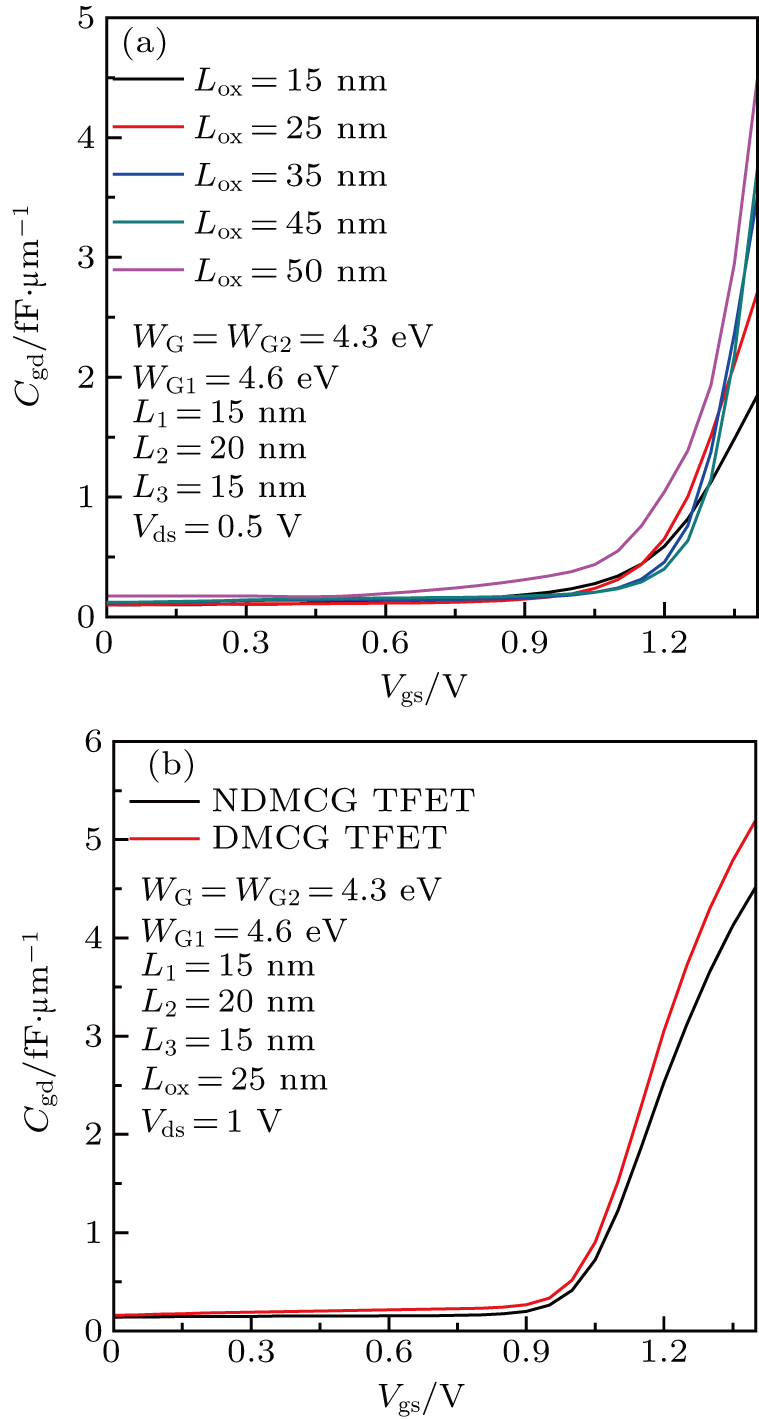

This subsection is dedicated to the study of the influence of variation in L3, and L1 on the gate–drain capacitance (Cgd) of NDMCG TFET as depicted in Fig.

Figure

| Fig. 8. (a) Cgd–Vgs curves for NDMCG TFET with different values of Lox, and (b) comparison of Cgd–Vgs curve between NDMCG TFET and DMCG TFET. |

Further, RF parameters of gain bandwidth product (GBP), cut-off frequency (ft), transit time (τ), and transconductance frequency product (TFP) are analyzed. The GBP determines the maximum working frequency for a direct current gain of 10, and the formula of GBP is

| Fig. 9. Curves of (a) GBP, (b) ft, (c) τ, and (d) TFP versus Vgs of NDMCG TFET for different values of L3. |

Transit time (τ) is defined as the time taken for carriers to flow from source to drain region, and it is also another important parameter to confirm the NDMCG TFET for high-frequency operation, which is expressed as

| Fig. 10. Curves of (a) GBP, (b) ft, (c) τ, and (d) TFP versus Vgs for NDMCG TFET with different values of L1. |

Figure

| Fig. 11. Curves of (a) GBP, (b) ft, (c) τ, and (d) TFP versus Vgs for NDMCG TFET with different values of Lox. |

Figure

| Fig. 12. Comparison of curves of (a) GBP, (b) ft, τ, and (c) TFP versus Vgs between NDMCG TFET and DMCG TFET, with Vds fixed at 1 V. |

The above-mentioned parasitic capacitance and RF parameters for TFETs are analyzed when Vds is 1 V, and the maximum values for GBP, ft, and TFP are achieved when Vgs is nearly 1.1 V. However, according to the projection of International Technology Roadmap for Semiconductor (ITRS), the TFET has a great potential for low-power applications. In this case, Vds is lower than 1 V. Therefore, the device optimization is also analyzed when Vds is fixed at 0.5 V as indicated in Fig.

The performances of NDMCG TFET are studied based on TCAD simulations. We demonstrate that the increase of Lox affects Iamb, but has little effect on Ion and Ioff. The results show that the design of a non-uniform gate–oxide layer with Lox being 35 nm and the dual-material control-gate lengths L1, L2, and L3 being respectively 15, 20, 15 nm can realize high Ion/Ioff and RF parameters with relatively low value of Iamb. When the drain–source voltage is fixed at 1 V for the optimized device, the RF parameters GBP, ft, and TFP are investigated, of which the maximum values are 199 GHz, 1.2 THz, and 6.1 THz, respectively. Moreover, the RF parameters of the NDMCG TFET are enhanced compared with those of the conventional DMCG TFET under lower power supply voltage. The results indicate that the NDMCG TFET has the great potential applications in high-performance RF component, which should be the superiority in future high-frequency, and high-switching-speed electronics applications.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 | |

| 16 | |

| 17 | |

| 18 | |

| 19 | |

| 20 | |

| 21 | |

| 22 | |

| 23 | |

| 24 | |

| 25 | |

| 26 | |

| 27 | |

| 28 | |

| 29 | |

| 30 | |

| 31 | |

| 32 | |

| 33 | |

| 34 | |

| 35 |