† Corresponding author. E-mail:

We present a new charge trapping memory (CTM) device with the Au/Ga2O3/SiO2/Si structure, which is fabricated by using the magnetron sputtering, high-temperature annealing, and vacuum evaporation techniques. Transmission electron microscopy diagrams show that the thickness of the SiO2 tunneling layer can be controlled by the annealing temperature. When the devices are annealed at 760 °C, the measured C–V hysteresis curves exhibit a maximum 6 V memory window under a ±13 V sweeping voltage. In addition, a slight degradation of the device voltage and capacitance indicates the robust retention properties of flat-band voltage and high/low state capacitance. These distinctive advantages are attributed to oxygen vacancies and inter-diffusion layers, which play a critical role in the charge trapping process.

Some new types of memory have attracted extensive attention from researchers.[1–3] In particular, charge trapping memory (CTM) is receiving more and more attention due to its strong charge trapping capability, good durability, and low program/erase voltages.[4–6] However, technology scaling is a major obstacle to improve the memory performance and capacity of modern CTMs.[7, 8] As the size of the CTM device shrinks, the charge trapping efficiency decreases. In addition, as the charge tunnel breaks down due to thinner trapping or blocking layers, the trade-off between data retention and access time cannot be balanced,[9] and the crosstalk between adjacent floating gates is gradually increasing.[10] To address these challenges, scientists have developed a variety of new CTM devices. For example, the structures of ZrO2/Al2O3/ZrO2 and HfO2/Al2O3/HfO2 have outstanding performance due to their strong charge trapping capability and fast programming speed associated with high-k materials.[11–16] In addition, fast and high-density oxide materials for non-volatile memories have been studied for a long time because of their robust switching mechanisms and storage immunities to read disturbances.[19–23] There are also many studies on two-dimensional (e.g., WS2, graphene, MoS2) and oxide materials (e.g., HfO2, Al2O3, ZrO2) used for memory, which can improve the memory properties.[2, 11–14, 36] Moreover, one well-developed oxide layer as charge trapping and blocking layers has shown great potential in recent years.[24–26] Ga2O3 is a wide bandgap semiconductor material with numerous physical properties, such as electrical conductivity and luminescence, which is widely used in photodiodes, thin film electroluminescent devices, and ultraviolet detectors.[15–18]

In this study, we explored the Ga2O3 film as charge trapping and blocking layers in CTMs. Particularly, we studied the charge storage and data retention characteristics of CTMs based on an Au/Ga2O3/SiO2/Si structure. Magnetron sputtering, high-temperature annealing, and vacuum evaporation techniques were adopted to prepare the device samples. Memory windows of the fabricated the Ga2O3 samples were measured after annealing at different temperatures. The largest memory window is found to correspond to an annealing temperature of 760 °C. Transmission electron microscopy (TEM) analysis shows that the thickness of the SiO2 tunneling layer varies with the annealing temperature, indicating that the annealing temperature changes the charge storage capability. The measured long-term retention of flat-band voltage and high/low state capacitances also demonstrates that this proposed device has excellent retention characteristics as a charge trapping memory.

A (100)-oriented p-type silicon was in turn immersed in deionized water, acetone, and alcohol. Next, it was placed in an ultrasonic cleaner for 5 min and then immersed in a diluted hydrogen fluoride solution (1%) for 90 s. Then, it was soaked in deionized water and placed in an ultrasonic cleaner for 5 min. A 70 nm-thick Ga2O3 film was sputtered on the Si substrate for 140 min under 3 Pa, 80 W, and Ar: O2=25: 25. Then, rapid high-temperature annealing was performed for 5 min at 600 °C, 680 °C, 760 °C, and 780 °C in the 35 sccm O2 gas environment, respectively. Finally, Au electrodes with a thickness of 80 nm were grown by vacuum evaporation. After these device samples were fabricated, memory storage windows and high/low state capacitances for each annealing temperature were tested by the Keithley 4200 SCS. The relationship between the annealing temperature and the thickness of the SiO2 tunneling layer was investigated using the TEM. Meanwhile, the x-ray photoelectron spectroscopy (XPS) of various etching depths was used to analyze the CTM memory mechanism.

Figure

| Fig. 1. (a) Schematic view of the Au/Ga2O3/SiO2/Si structure, (b) C–V curves of the fabricated samples with different annealing temperatures. |

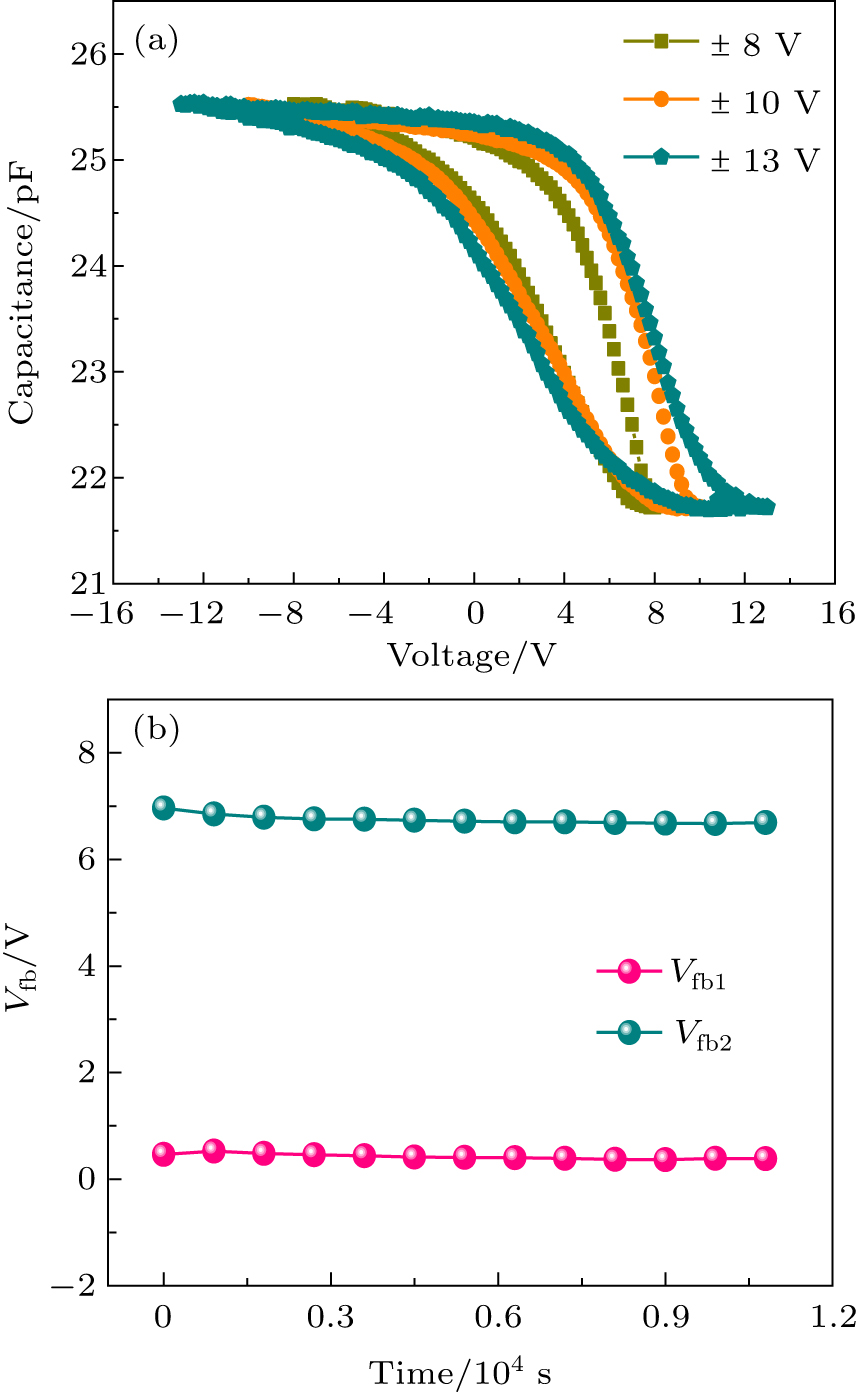

The device annealed at 760 °C was selected and applied with different scanning gate voltages to measure the C–V curves. As shown in Fig.

| Fig. 2. (a) The C–V curves with different scan voltages and (b) the flat band voltage retention of the fabricated sample with 760 °C annealing. |

The planar charge trapping density per unit area (Nt) is estimated as[29, 30]

|

Data retention property of the flat-band voltage is another important metric to characterize the memory performance. The device changes from a low capacitance state to a high capacitance state during a ±13 V sweep. Then, a small area near the flat-band voltage is selected every 15 min for C–V scanning. This voltage range is not charged or trapped in the C–V measurements. Similarly, a voltage of −13 V to +13 V shifts the device from a high capacitance state to a low capacitance state. As shown in Fig.

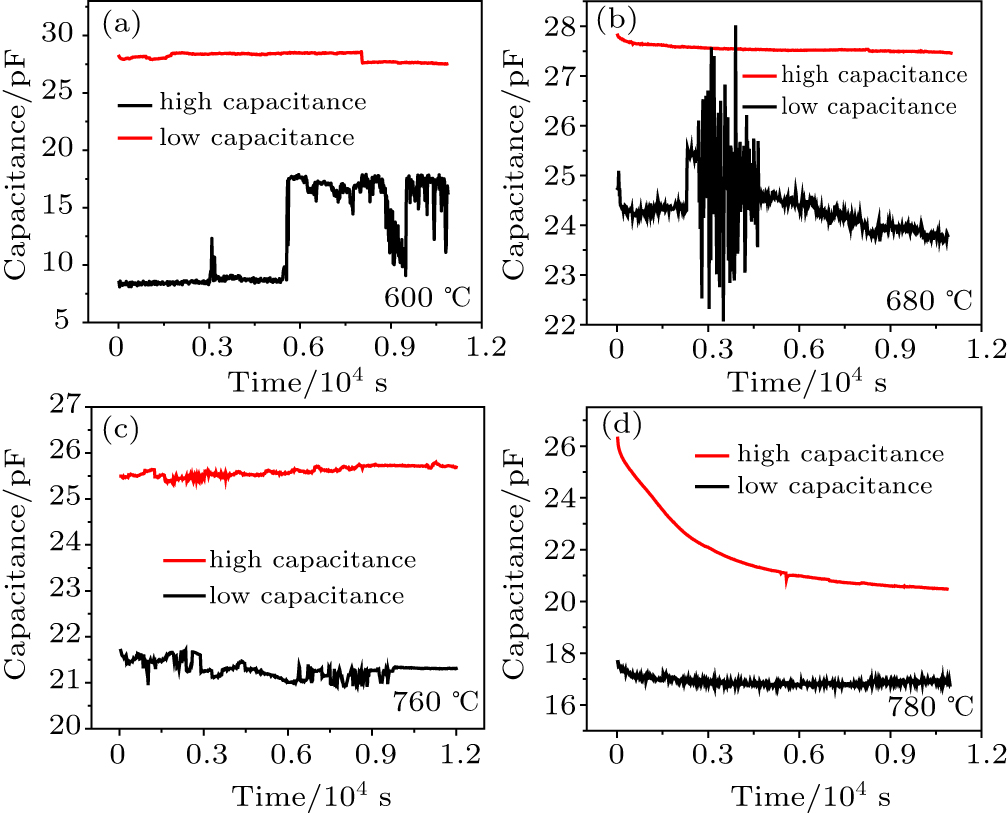

In order to in-depth investigate the data retention property, the capacitance retention was also tested for the device annealed at different annealing temperatures. As shown in Fig.

| Fig. 3. Long-term retention measurement of the high/low state capacitances for CTM devices annealed at (a) 600 °C, (b) 680 °C, (c) 760 °C, and (d) 780 °C, respectively. |

The CTM device based on the 760 °C annealing has such excellent performance, which is originated from oxygen vacancies and an inter-diffusion layer that improves the charge trapping capability.[9, 35] To further confirm the memory mechanism, its microscopic characterization analysis was studied by TEM and XPS in detail. Figure

| Fig. 4. Cross-sectional TEM images of Au/Ga2O3/SiO2/Si structures annealed at (a) 600 °C, (a) 680 °C, (a) 760 °C, and (a) 780 °C. |

Figure

In summary, we have studied the charge storage and data retention characteristics of the CTM device with an Au/Ga2O3/SiO2/Si structure. The memory storage windows vary with annealing temperatures, and the largest memory window is 6 V resulted from an annealing temperature of 760 °C. At a working voltage range of ±13 V, the planar charge trapping density of this CTM device is approximately 7.6×1011 cm−2. After about 104 s of device testing, the degradation of high and low state capacitances is 1% and 1.7%, respectively. These properties are attributed to the oxygen vacancies and the inter-diffusion layer of Ga2O3 and SiO2. This proposed Au/Ga2O3/SiO2/Si structure is promising for the next-generation of CTM devices.

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] | |

| [20] | |

| [21] | |

| [22] | |

| [23] | |

| [24] | |

| [25] | |

| [26] | |

| [27] | |

| [28] | |

| [29] | |

| [30] | |

| [31] | |

| [32] | |

| [33] | |

| [34] | |

| [35] | |

| [36] |