Project supported by the National Natural Science Foundation of China (Grant No. 61704130), the Fundamental Research Funds for the Central Universities, China (Grant No. 20101166085) and the Opening Project of Key Laboratory of Microelectronic Devices & Integrated Technology from Institute of Microelectronics, Chinese Academy of Sciences (Grant No. 90109162905).

Project supported by the National Natural Science Foundation of China (Grant No. 61704130), the Fundamental Research Funds for the Central Universities, China (Grant No. 20101166085) and the Opening Project of Key Laboratory of Microelectronic Devices & Integrated Technology from Institute of Microelectronics, Chinese Academy of Sciences (Grant No. 90109162905).

† Corresponding author. E-mail:

Project supported by the National Natural Science Foundation of China (Grant No. 61704130), the Fundamental Research Funds for the Central Universities, China (Grant No. 20101166085) and the Opening Project of Key Laboratory of Microelectronic Devices & Integrated Technology from Institute of Microelectronics, Chinese Academy of Sciences (Grant No. 90109162905).

In this paper, a novel junctionless field effect transistor (JLFET) is proposed. In the presence of a field plate between gate and drain, the gate-induced drain leakage (GIDL) effect is suppressed due to the decrease of lateral band-to-band tunneling probability. Thus, the off-state current Ioff, which is mainly provided by the GIDL current, is reduced. Sentaurus simulation shows that the Ioff of the new optimized JLFET is reduced by ∼ 2 orders and its sub-threshold swing can reach 76.8 mV/decade with little influence on its on-state current Ion, so its Ion/Ioff ratio is improved by 2 orders of magnitude compared with that of the normal JLFET. Optimization of device parameters such as Φfps (the work difference between field plate and substrate) and LFP (the length of field plate), is also discussed in detail.

In the down-scaling approach, conventional Si metallic-oxide semiconductor field-effect transistors (MOSFETs) are approaching towards the end of the technology roadmap.[1–3] One of the main reasons is that the rapid down-scaling of conventional bulk MOSFETs below 45 nm requires an ultrasteep doping profile at the metallurgical junction and a high thermal budget corresponding to the post-anneal dopant activation, which leads to extreme troubles in device fabrication.[4,5] To overcome this limitation, various alternative devices are being proposed, and a new class of field effect device called the junctionless field-effect transistor (JLFET) has attract lots of research attention in recent years.[6–14]

The basic structure of a JLFET consists of a uniformly highly doped silicon channel controlled by at least an on gate electrode. Unlike “regular” junction-based FETs, in JLFET, both the source and the drain have the same type of doping as the channel, and there is no pn junction. The principle of JLFET operation is also quite different as it counts on majority carriers instead of minority carriers. Moreover, the current flows mainly in the volume and is no longer confined at the Si/SiO2 interface. Based on these specific conduction mechanisms, JLFET has a large on-state current Ion and an excellent drive capability, which could be improved by increasing the doping concentration.

However, high doping will increase not only the on-state current Ion but also the off-state current Ioff, thus affecting the ratio of Ion over Ioff.[15–17] Furthermore, above certain doping levels, the device could not be switched off even at the off state of the device. As in conventional MOSFET, the off-state current Ioff in JLFET is mainly caused by the gate-induced drain leakage (GIDL) effect at the gate edge between gate and drain.[18–20] Since the efficient gate control over the channel region leads to a considerable overlap of the valence band with the conduction band at the channel–drain interface, a lateral band-to-band tunneling (L-BTBT) of electrons from the channel region to the drain region in the off-state (VGS = 0 V), which is a dominant mechanism for GIDL in JLFET. In order to reduce Ioff, several device structures have been designed, such as JLFET with dielectric pocket double gate,[21] JLFET with hybrid channel,[22] JLFET with core-shell architecture,[23] etc.

In this paper, we propose a novel JFELT with field plate structure to reduce the high field effect at the gate edge, finally suppressing the GIDL effect and Ioff. The TCAD simulation indicates that Ioff of the new optimized JLFET is reduced by ∼ 2 orders and its sub-threshold swing can reach 76.8 mV/decade with little affection on its Ion, so its Ion/Ioff ratio is improved by 2 orders of magnitude over the normal JLFET. Optimization of device parameters such as Φfps (the work difference between field plate and Si) and LFP (the length of field plate) is also discussed in detail.

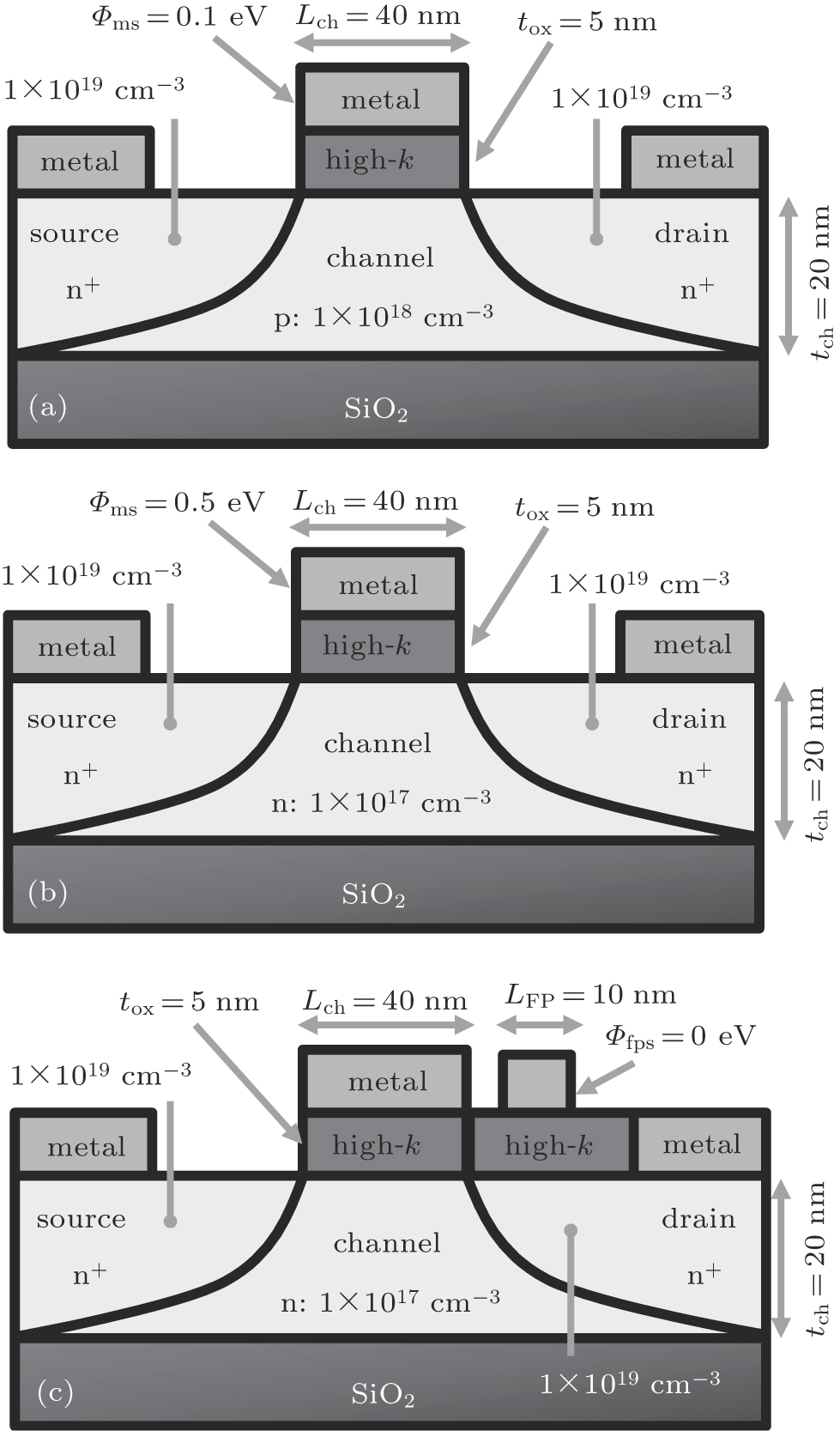

The schematic views of the conventional MOSFET, the normal JLFET, and the novel JFLET (FP JLFET) are shown in Figs.

Sentaurus TCAD was used to perform the device simulations. The field-dependent and doping dependent mobility degradations were considered using the Philips unified mobility model and Lombardi mobility model. Bandgap narrowing, Shockley–Read–Hall, the Auger recombination model, and Fermi–Dirac statistics were also involved. A nonlocal BTBT model was used to account for the lateral tunneling of the GIDL effect. A temperature of 300 K was employed in simulations.

Figure

| Fig. 2. (color online) Plots of electric field along the vertical direction of the channel underneath the gate in the off-state (VDS = 1.0 V, VGS = 0 V), with inset showing GBTBT near the gate edge. |

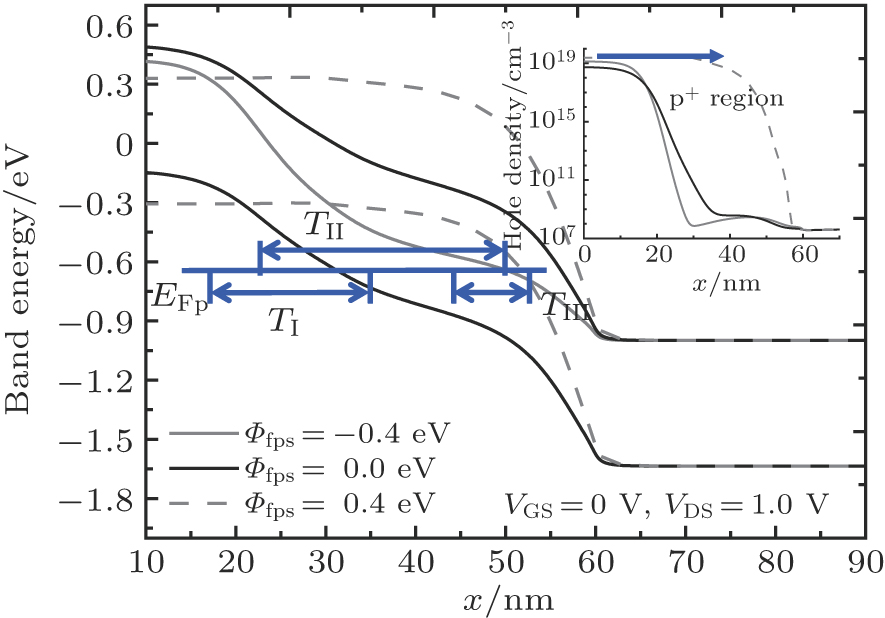

| Fig. 3. (color online) Energy bands along the parallel directions of channels of JLFET and FP JLFET underneath the gate, in off-state (VDS = 1.0 V, VGS = 0 V). |

Figure

The transfer characteristics of the new FP JLFET and normal JLFET (VDS = 1 V) are shown in Fig.

Also from Fig.

To study the influence of Φfps on GIDL and the electrical characteristics of FP JLFET, the ID–VG curves with various values of Φfps were simulated as shown in Figs.

Also from Fig.

To understand the phenomenon above, the energy bands along the parallel direction of the FP JLFET with various values of Φfps (Φfps = −0.4 eV, 0.0 eV, and 0.4 eV) in the off-state are examined as shown in Fig.

Another important parameter affecting the off-state current of the FP JLFET is LFP. Figure

In this work, we have proposed a JLFET with a field plate for significantly improving the off-state performance. Using Sentaurus simulations, we demonstrate that the field plate in the new device can effectively broaden the tunneling barrier width at the drain-channel interface, resulting in the occurrence of insufficient band bending for L-BTBT and thus restricting the GIDL effect in the new JLFET. Therefore, the proposed device architecture provides the off-state current reduced by 2 orders of magnitude without deteriorating the on-state current, resulting in a significant Ion/Ioff ration enhancement compared with the scenario of the conventional JLFET. Our results may promote the experimental realization of this structure.

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] | |

| [20] | |

| [21] | |

| [22] | |

| [23] | |

| [24] | |

| [25] | |

| [26] |