† Corresponding author. E-mail:

Project supported by the National Natural Science Foundation of China (Grant Nos. 61404005, 61421005, and 91434201).

In this work, the trap-assisted tunneling (TAT) mechanism is modeled as a two-step physical process for charge trapping memory (CTM). The influence of the TAT mechanism on CTM performance is investigated in consideration of various trap positions and energy levels. For the simulated CTM structure, simulation results indicate that the positions of oxide traps related to the maximum TAT current contribution shift towards the substrate interface and charge storage layer interface during time evolutions in programming and retention operations, respectively. Lower programming voltage and retention operations under higher temperature are found to be more sensitive to tunneling oxide degradation.

In the past few years we have seen the explosive growth of the non-volatile semiconductor memory market because of the unceasing demand for higher memory density and lower bit cost.[1] During the aggressive scaling of flash memory technology, the floating gate structure has faced great challenges from both technological and physical limitations, such as reducing coupling ratio, cell-to-cell interference, and increasing gate leakage current.[2] In order to continue the scaling trend, great effort has been devoted to developing next-generation memory structures.[3–6] Among these structures, the charge trapping memory (CTM) shows the most excellent potential as one of the most promising candidates for future memory solutions.[7–9] Furthermore, in recent years, high-density CTM in three-dimensional (3D) architectures for the NAND applications has drawn a great deal of attention.[10–12]

Under this circumstance, understanding the physical mechanisms in CTM has growing importance in terms of designing and optimizing CTM devices. The trap-assisted tunneling (TAT) is one of the most important mechanisms influencing the memory performance. On the one hand, TAT is an indispensable part of the tunneling current due to the existence of intrinsic defects in oxide layers. An accurate calculation of TAT current is crucial for achieving high accuracy in modeling CTM performance. On the other hand, it is largely accepted that electrical stress in the tunneling oxide during program/erase (P/E) cycle leads to the generation of interface defects and bulk traps in oxide layers.[13,14] In this regard, the TAT mechanism is related to reliability issues of the memory cells after P/E cycle, leading to a variation of memory characteristics. Especially, degradation in tunneling oxide can cause the increase in charge loss during retention operation. However, previous studies on modeling the TAT mechanism mainly focused on the gate leakage current of the MOS structure.[15–17] Only little work has addressed the TAT effect in the context of flash memory cells.[18,19]

In this paper, the TAT mechanism in CTM cells is carefully modeled and implemented in the developed simulator[20–22] for NAND flash memory. The influence of the TAT mechanism on CTM performance is investigated in consideration of various oxide trap positions and energy levels. The programming and retention performances of CTM after P/E cycle are also evaluated.

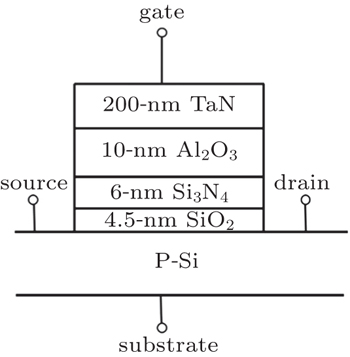

The device structure we used to evaluate the influence of TAT on CTM performance is a standard CTM cell with 4.5-nm/6-nm/10-nm (SiO2/Si3N4/Al2O3) gate stacks as shown in Fig.

| Fig. 1. Schematic illustration of the simulated standard CTM cell with a 4.5/6/10 nm (SiO2/Si3N4/Al2O3) gate stack. |

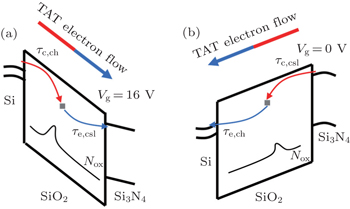

The TAT mechanism is modeled as a two-step process,[23] i.e., the electron capture and emission of the oxide traps. The TAT current driven through each oxide trap is given by the capture and emission times for each trap, τc,ch/csl and τe/csl respectively, considered from the charge reservoir, i.e., channel or charge storage layer as schematically illustrated in Fig.

| Fig. 2. Schematics of the capture and emission time constants for calculating TAT current in (a) programming and (b) retention operations. |

Accumulating the current-density contributions from the traps in a small interval dx at each distance x, the total TAT current density through the entire oxide layer is expressed as

It should be mentioned that the calculations of capture and emission coefficients are related to the energetic position of ET with respect to the energy level E in the integration. When ET is lower than E, the capture coefficient is energy-independent and can be written as

In order to improve calculation efficiency, an approximation is made to solve the above complicated integral by assuming E = Ec for calculating the time constants.[24] Overall, using Eqs. (

The abovementioned physical model accounting for the TAT mechanism has been incorporated into our calibrated two-dimensional (2D) self-consistent CTM simulator,[21] which carefully takes into consideration the DT/FN tunneling process, charge trapped/de-trapping mechanisms, and drift-diffusion transport in the gate stack of memory cells. In addition, oxide traps with arbitrary energy level and spatial distribution are considered in the simulation. The main parameters adopted in the simulation are summarized in Table

| Table 1. Main parameters for the simulation. . |

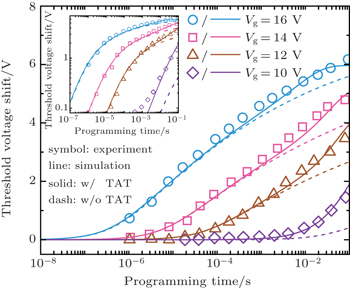

In order to obtain an overview of the influences of the TAT mechanism on programming and retention characteristics of CTM cells, we first perform the simulations in the cases with and without considering the TAT effect. In addition to the TAT mechanism, in the simulation the direct and FN tunneling process within the tunneling oxide are taken into consideration. Comparisons between simulation prediction and experimental measurement are also made. Figure

| Fig. 3. Comparison between experimental programming data and simulation results of CTM cells and influence of TAT on programming characteristics. |

| Fig. 4. Comparison between experimental retention and simulation predictions of CTM cells under different temperatures and influence of TAT on retention characteristics. |

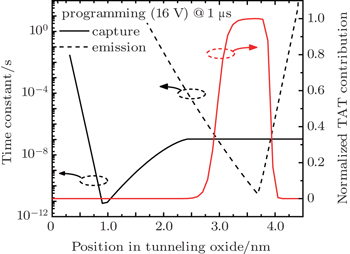

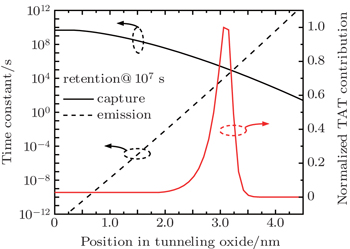

The defect traps allow an extra tunneling path in the oxides, but not all traps have equivalent contribution to TAT current. From Eq. (

| Fig. 5. Capture and emission time constants used to calculate TAT current density along tunneling oxide and the related normalized TAT current contribution under 16-V programming voltage at 1 μs. |

| Fig. 6. Capture and emission time constants used to calculate TAT current density along tunneling oxide and the related normalized TAT current contribution for 375-K retention simulation at 107 s. |

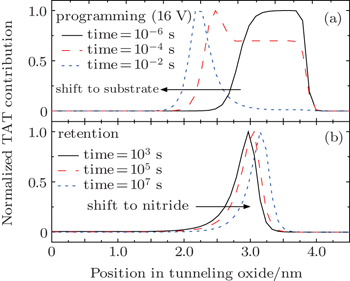

However, the positions of peak contribution to the overall TAT current are variable with time evolution under programming and retention operations as shown in Fig.

| Fig. 7. The variations of normalized TAT contribution with position in tunneling oxide with time evolution in (a) programming and (b) retention operations. |

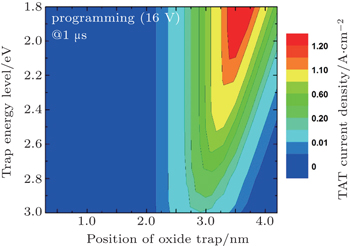

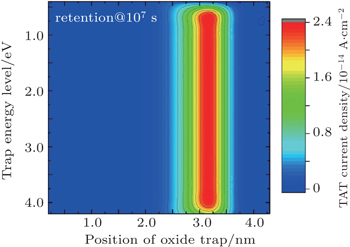

Apart from the position of oxide defects, trap energy level is another major factor to determine TAT current. To investigate the influences of the trap energy level and spatial position on TAT current density, we assume that the trap distribution in tunneling oxide has a Gaussian distribution with a peak value of 7 × 1018 cm− 3 and a small standard deviation of 0.2 nm. Simulations of devices with various peak positions and trap energy levels are performed. Figure

| Fig. 8. TAT current densities under 16-V programming voltage at 1 μs of devices with various peak positions and trap energy levels. |

| Fig. 9. TAT current densities at 107 s of retention operation under 360-K temperature of devices with various peak positions and trap energy levels. |

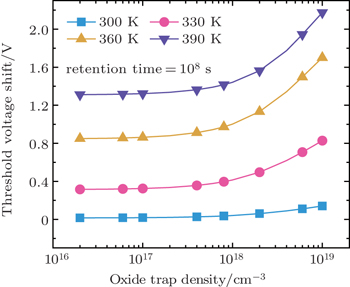

During P/E operations, the electric field in tunneling oxide can typically exceed 10 MV/cm.[31] A Large number of P/E cycles leads to the generation of oxide traps and thus causes reliability issues of CTM cells. The influences of TAT on programming and retention operations are strongly correlated with trap density in tunneling oxide. Figure

| Fig. 10. Programming speeds under different programming voltages with increasing the level of tunneling oxide degradation. |

In this paper, we carefully model TAT mechanism in CTM cells and evaluate the influences of TAT on programming and retention characteristics. Our results indicate that the TAT mechanism is a critical factor for CTM operations, especially at low tunneling oxide fields. The influence of the TAT mechanism on CTM performance is investigated in consideration of various trap positions and energy levels in the tunneling oxide.

The results show that only the oxide traps at a small distance are related to a major contribution to TAT current. In addition, the positions corresponding to the maximum contribution shift towards the substrate interface and the charge storage layer interface during programming and retention operations, respectively. Lower programming voltage and retention operations under higher temperature are more sensitive to tunneling oxide degradation.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 | |

| 16 | |

| 17 | |

| 18 | |

| 19 | |

| 20 | |

| 21 | |

| 22 | |

| 23 | |

| 24 | |

| 25 | |

| 26 | |

| 27 | |

| 28 | |

| 29 | |

| 30 | |

| 31 |