† Corresponding author. E-mail:

‡ Corresponding author. E-mail:

Project supported by the National Natural Science Foundation of China (Grant Nos. 61376096, 61327813, and 61404126) and the National Basic Research Program of China (Grant No. 2010CB934104).

Silicon junctionless nanowire transistor (JNT) is fabricated by femtosecond laser direct writing on a heavily n-doped SOI substrate. The performances of the transistor, i.e., current drive, threshold voltage, subthreshold swing (SS), and electron mobility are evaluated. The device shows good gate control ability and low-temperature instability in a temperature range from 10 K to 300 K. The drain currents increasing by steps with the gate voltage are clearly observed from 10 K to 50 K, which is attributed to the electron transport through one-dimensional (1D) subbands formed in the nanowire. Besides, the device exhibits a better low-field electron mobility of 290 cm2·V−1·s−1, implying that the silicon nanowires fabricated by femtosecond laser have good electrical properties. This approach provides a potential application for nanoscale device patterning.

The rapid downscaling of metal–oxide–semiconductor field-effect transistors (MOSFETs) has posed increasing challenges such as short channel effect and degenerated carrier mobility. In particular, the ultrasharp pn junction with extremely high doping gradients becomes difficult to manufacture as the gate length is reduced down to 10 nm or even less. The junctionless nanowire transistor (JNT) has been recently proposed as a promising alternative to a new generation of transistors.[1,2] The doping concentration of JNT is uniform through the source, channel and drain. The current flows through the bulk of the channel as opposed to just along the surface in comparison with junction-based inversion-mode MOSFET. Consequently, JNT exhibits more excellent electrical performances. The key to fabricating JNT is the formation of an ultra-narrow channel to ensure the full depletion of carriers under zero gate voltage.

For decades, photolithography has been the predominant method of fabricating MOSFETs. Photolithography uses light to transfer a patterned feature from a photomask to photoresist on semiconductor wafer. Since the cost for lithographic equipment and photomask sets keeps rising with each technology generation, alternative cheaper patterning techniques are urgently required. The nanofabrication utilizing laser as an energy source has a multitude of advantages including maskless, three dimensions, high resolution and rapid prototyping,[3,4] providing an attractive method for nanoscale patterning applications. Early experimental results showed that the nanostructures fabricated by laser ablation always have thermal damages. However, femtosecond laser lithography can transform the photoresist by absorbing one or multiple phonons, which will dramatically reduce the thermal damages. In this approach, the focused femtosecond laser is directly used to write the desired image into the photoresist without lithographic mask. Thus, it offers great flexibility due to its maskless and discretionary nature. Previous theoretical and experimental results have proved that the multiphoton nanofabrication has the potential to exceed the diffraction limit.[5] Besides, the interaction between the femtosecond laser and the material occurs only in the vicinity of focal spot, leaving material surface intact. This manufacturing technique has been successfully utilized to fabricate nanoscale dot arrays and lines in silicon wafers.[6,7]

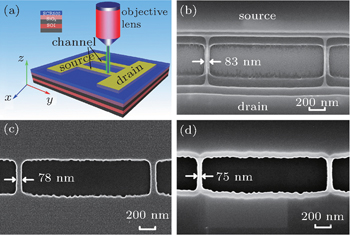

In this paper, we demonstrate the experimental results of JNT fabricated by femtosecond laser two-photon lithography. Two laser beams are focused by an optical lens system to be a writing spot on the wafer surface, which provides the optical energy for transforming the photoresist. Two dry etching processes are implemented to transfer the desired image from the negative SCR500 resin onto the top silicon layer. The fabricated JNT exhibits good gate control ability, large electron mobility, and good low-temperature instability.

The starting material was a (100)-oriented SOI wafer with a 55-nm-thick top silicon and a 145-nm-thick buried oxide. Two laser beams with the peak wavelengths of 800 nm and 400 nm were utilized to fabricate the device. The pulse width and repetition rate were 100 fs and 82 MHz, respectively. The top silicon layer was uniform heavily doped by phosphorus ion implantation with a dose of 5 × 1013 cm−2, leading to a doping concentration of 1 × 1019 cm−3. It was followed by depositing a 50-nm-thick SiO2 layer on the top of SOI substrate. The SiO2 layer was chosen to minimize the standing wave effect of the femtosecond laser.[8] Afterwards, femtosecond laser lithography with optimized laser powers of 3.38 mW for 800 nm laser and 2.02 μW for 400 nm laser was utilized to linearly pattern twin nanowires connecting two pads, as illustrated in Fig.

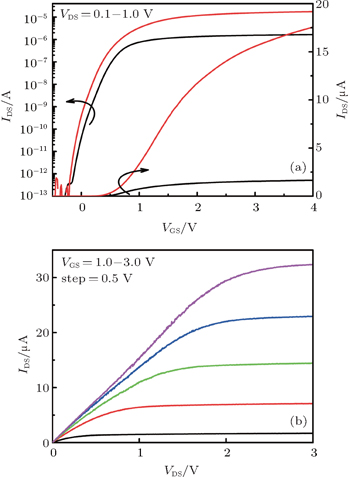

The electrical characteristics of JNT are characterized by Agilent B1500 semiconductor parameter analyzer. Low temperature characterizations are carried out by Lakershore-340 temperature controller under high vacuum. At room temperature, the silicon JNT exhibits good transfer and output characteristics. The curves of drain current IDS versus gate voltage VGS in Fig.

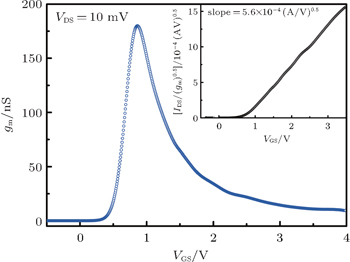

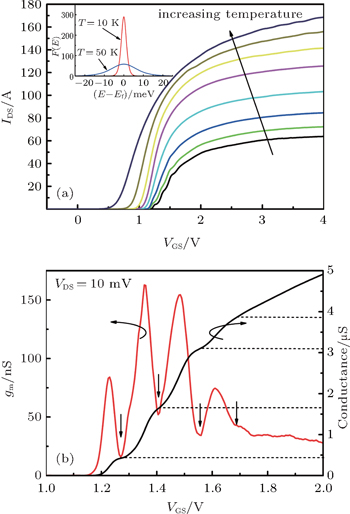

The plot of the extracted transconductance (gm = ∂IDS/∂VGS) versus VGS from transfer characteristics at VDS = 10 mV is shown in Fig.

Next, we focus on the temperature-dependent transport of JNT. When the temperature is reduced, the interesting electrical results are observed. Figure

| Fig. 4. (a) Plots of measured IDS versus VGS at different temperatures (10 K, 20 K, 50 K, 100 K, 150 K, 200 K, 250 K, and 300 K) and VDS = 10 mV. The insert shows thermal broadening functions[15] at 10 K and 50 K. The energy distribution of electrons at 10 K is significantly narrower. (b) Conductance and transconductance characteristics of JNT measured at 10 K with VDS = 10 mV. |

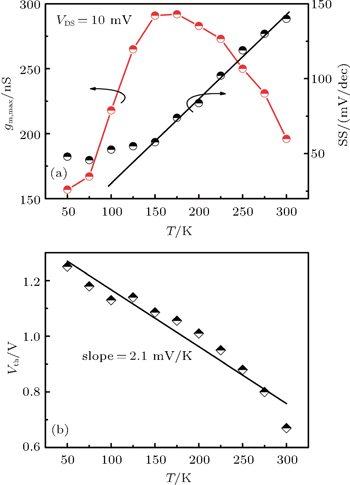

Any variation of temperature will induce the change of electrical parameters of JNT device, such as the threshold voltage, flatband voltage, subthreshold swing and electron mobility. Temperature instabilities of some electrical parameters are investigated in a temperature range from 50 K to 300 K.

The left curve of Fig.

| Fig. 5. (a) Temperature-dependent SS and the maximum gm. (b) Experimental Vth of JNT as a function of temperature. The applied VDS equals 10 mV. |

Figure

In this work, the JNT with the physical channel cross-section area of 28 nm×55 nm is fabricated by femtosecond laser lithography. The extracted low-field electron mobility is 290 cm2·V−1·s−1, inferring that this method can well impede the damage of the crystalline structure of silicon. Besides, the increase of current steps with gate voltage is clearly observed at a temperature of 10 K, which is attributed to the electron transport through degenerated 1D subbands formed in the nanowire. The mobility is phonon limited at temperatures larger than 175 K, while it appears to be limited by impurity scattering below that temperature. The slope of threshold voltage shift with the temperature is 2.1 mV/K due to the influence of interface traps. These results help us better understand the transport mechanism in JNT at low temperatures. The development of this novel maskless lithography has tremendous potential for opening a new market in nanoscale device fabrication. The low cost and high resolution process is expected to provide an accurate, repeatable and efficient means of creating nanoscale structures for device applications.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 | |

| 16 | |

| 17 | |

| 18 | |

| 19 | |

| 20 |