† Corresponding author. E-mail:

High-κ/Ge gate stack has recently attracted a great deal of attention as a potential candidate to replace planar silicon transistors for sub-22 generation. However, the desorption and volatilization of GeO hamper the development of Ge-based devices. To cope with this challenge, various techniques have been proposed to improve the high-κ/Ge interface. However, these techniques have not been developed perfectly yet to control the interface. Therefore, in this paper, we propose an improved stress relieved pre-oxide (SRPO) method to improve the thermodynamic stability of the high-κ/Ge interface. The x-ray photoelectron spectroscopy (XPS) and atomic force microscopy (AFM) results indicate that the GeO volatilization of the high-κ/Ge gate stack is efficiently suppressed after 500 °C annealing, and the electrical characteristics are greatly improved.

Recently, the high-κ/Ge gate stack with high-mobility substrates has been explored in order to continue to scale down the ultra-low power and high speed microelectronic devices.[1–3] One of the main concerns about high-κ/Ge gate stack devices is that Ge–O bonds inevitably exist at the interface between Ge and high-κ films and its volatilization occurs even below 500 °C, which is required for source/drain activation for the complementary metal–oxide semiconductor (CMOS) fabrication process.[4,5] Volatilization of GeO out of the air will generate a huge number of defects and traps in the high-κ film after GeO desorption and volatilization.[6,7] It tends to deteriorate the interface and high-κ film quality, leads to the gate leakage current largely increasing, mobility and reliabilities degrading obviously.[8,9] The mechanism of the GeO desorption is proposed to be that the interface oxygen vacancies generated at the GeO2/Ge interface diffuse into the GeO2 surface region.[10] Thus annealing the high-κ/Ge gate stacks without GeO desorption is the key process to realize a high-quality interface and high-κ film. To cope with this challenge, various techniques have been proposed to passivate the high-κ/Ge interface such as ultrathin Si or SiO2 capping layers,[11,12] GeOxNy passivation layer,[13] and high-quality GeO2 interfacial layers formed by plasma oxidation or ozone oxidation.[14–16] However, these techniques have not been developed perfectly yet to control the interface. Furthermore, some passivation layers have relatively low dielectric constants and may not enable scaling to low-EOT devices. Recently, a stress relieved pre-oxide (SRPO) treatment method is reported to improve the Si-based device characteristic and reduce the density of interfacial defects generated during the oxidation process.[17] Thus, in this paper, an improved SRPO treatment is investigated to improve the high-κ/Ge gate stack interface. The experimental results indicate that the improved SRPO treatment can suppress the GeO volatilization and improve the C–V characteristics of high-κ/Ge.

In Ref. [17], an SRPO treatment using H2O2 solution to form a 7.5-Å chemical oxidized SiO2 layer on Si and then an annealing treatment was performed for stress relief. Owing to the fact that GeO2 is hydrolysable in H2O, the SRPO treatment is improved in this work. Before the deposition, the p-type (100) Ge wafers each with a resistivity of 0.3 Ω·cm are dipped in dilute HF (hydrofluoric acid: deionized water = 1:500) to remove the Ge oxide. Then, in-situ oxidation of the Ge surface in the UV/ozone ProCleaner plus system is carried out to grow 1.5-nm GeO2. After that, these films are annealed in ozone/O2 mixed gas at 400 °C for 120 s and then cleaned by dilute HF to keep 1.5-nm GeO2. Finally, Ge substrates cleaned by the standard RCA method each have 1.5-nm GeO2 and these Ge substrates are immediately placed into the ALD chamber to deposited 4-nm HfO2 films. They are denoted as sample A and sample B, respectively. After the samples A and B annealed in the nitrogen at 500 °C for 60 s, the XPS measurements are carried out by using a Thermo Scientific K-alpha system. Electrical measurements are carried out using a Keithley 590 CV meter and a Keithley 4200-SCS system after the Al electrode has been fabricated by depositing 200-nm aluminum using electron-beam evaporation.

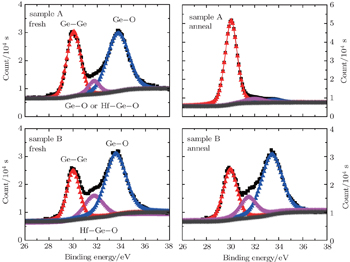

Figure

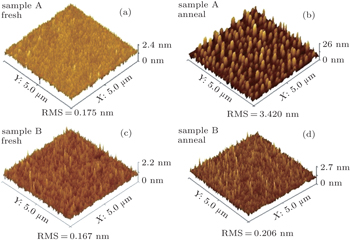

Since the fast desorption of GeO can form the thin film, the surface becomes rougher and rougher after GeO volatilization. The roughness of the surface can characterize the GeO volatilization intuitively as shown in Fig.

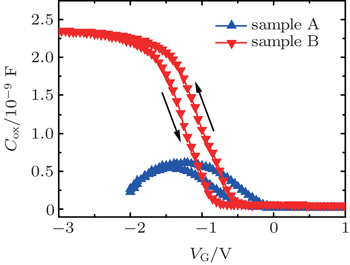

Figure

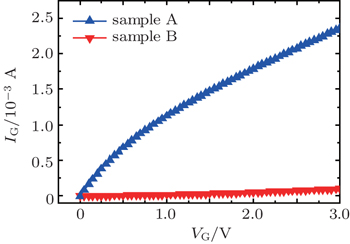

Figure

In this work, the electrical properties of high-κ film on Ge can be substantially improved by an improved SRPO pretreatment after annealing. The XPS results indicate that GeO volatilization occurs obviously for non-SRPO treated HfO2/Ge samples after annealing, whereas the improved SRPO treated samples show that the GeO volatilization is suppressed due to the fact that an efficient Hf germanate oxygen diffusion barrier is formed and shows a small RMS variation. The electrical measurement results indicate that the improved SRPO treated HfO2/Ge gate MOS structure presents a good C–V characteristic and the gate current decreases significantly compared with non-SRPO treated samples.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 | |

| 16 | |

| 17 | |

| 18 |