† Corresponding author. E-mail:

Total ionizing dose responses of different transistor geometries after being irradiated by 60Co γ-rays, in 0.13-

Silicon-on-insulator (SOI) technology has several intrinsic potential advantages over bulk silicon substrates due to the complete dielectric isolation of transistor, such as latch-up immunity, high speed and low power consumption, etc. In particular, the thin active silicon film provides better resistance against transient radiation effect like single event upset or dose rate encountered in the radiation environments.[1,2] But the thick buried oxide (BOX) introduces an additional constraint due to total ionizing dose (TID) effect.[2] Ionizing radiation can induce significant charge buildup in oxide and insulator, causing the device to degrade and fail to work.[3]

As device scaling, radiation-induced threshold voltage shift in MOSFET becomes negligible with gate oxide less than 5-nm thick,[4] because of less charges trapped in the thin oxide due to hole tunneling.[5] However, the shallow trench isolation (STI) oxide of deep submicron complementary metal–oxide–semiconductor (CMOS) technology does not scale down with the gate oxide thinning. As a result, radiation-induced charge trapped in the STI oxide leads to the source-drain or inter-diffusion leakage currents and radiation-induced narrow channel effect (RINCE), eventually limiting the radiation tolerance of conventional CMOS circuit.[6] Nevertheless, hardness-by-design (HBD) layout techniques like body tied to source (BTS) or H-shape gate transistor are an efficient method to shield the TID effect of the STI. But HBD layout techniques are not very broadly used in designing radiation-toleration application specific integrated circuits (ASICs) due to their own inherent disadvantages like large areas. Thus an enhanced susceptibility of transistor due to radiation-induced charge trapped in STI and the buried oxide is still a very interesting issue for space application.

During the past years, RINCE has been discussed widely in bulk technology.[6–10] However, few papers about RINCE in SOI technology have been published. References [11] and [12] focus on the threshold voltage shift and off-state leakage current, and reference [13] is devoted to the study of radiation-induced mobility degradation: in these studies there was a lack of a model to explain the said results. In this paper, we focus on using a mathematical model and TCAD simulations to investigate RINCE in 0.13-

All the devices used in our experiments were fabricated in 0.13-

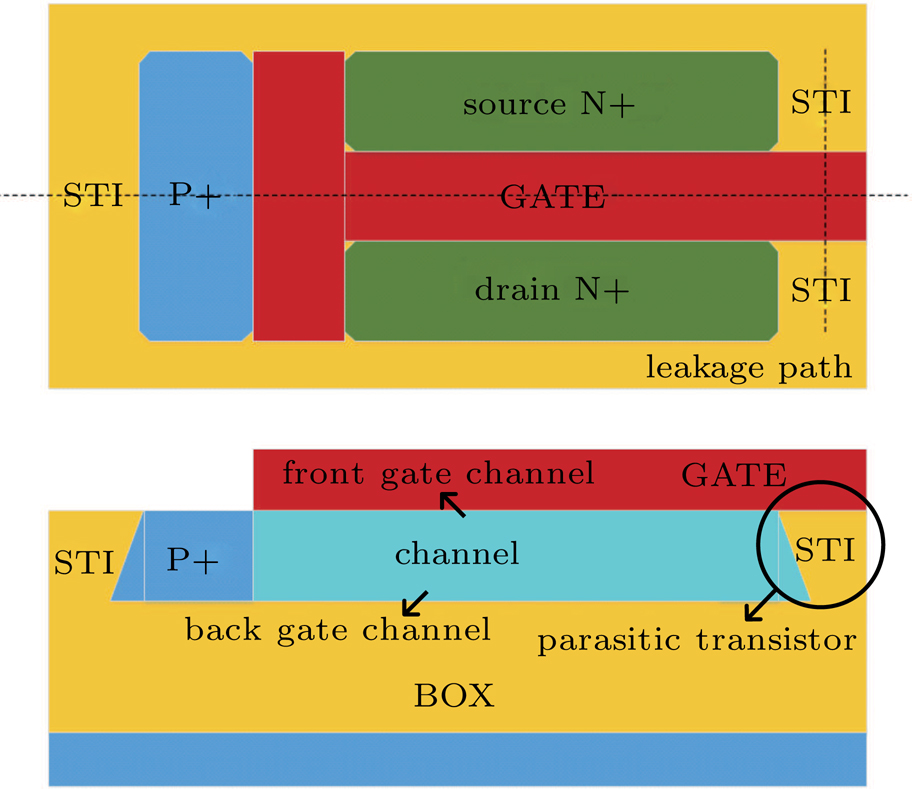

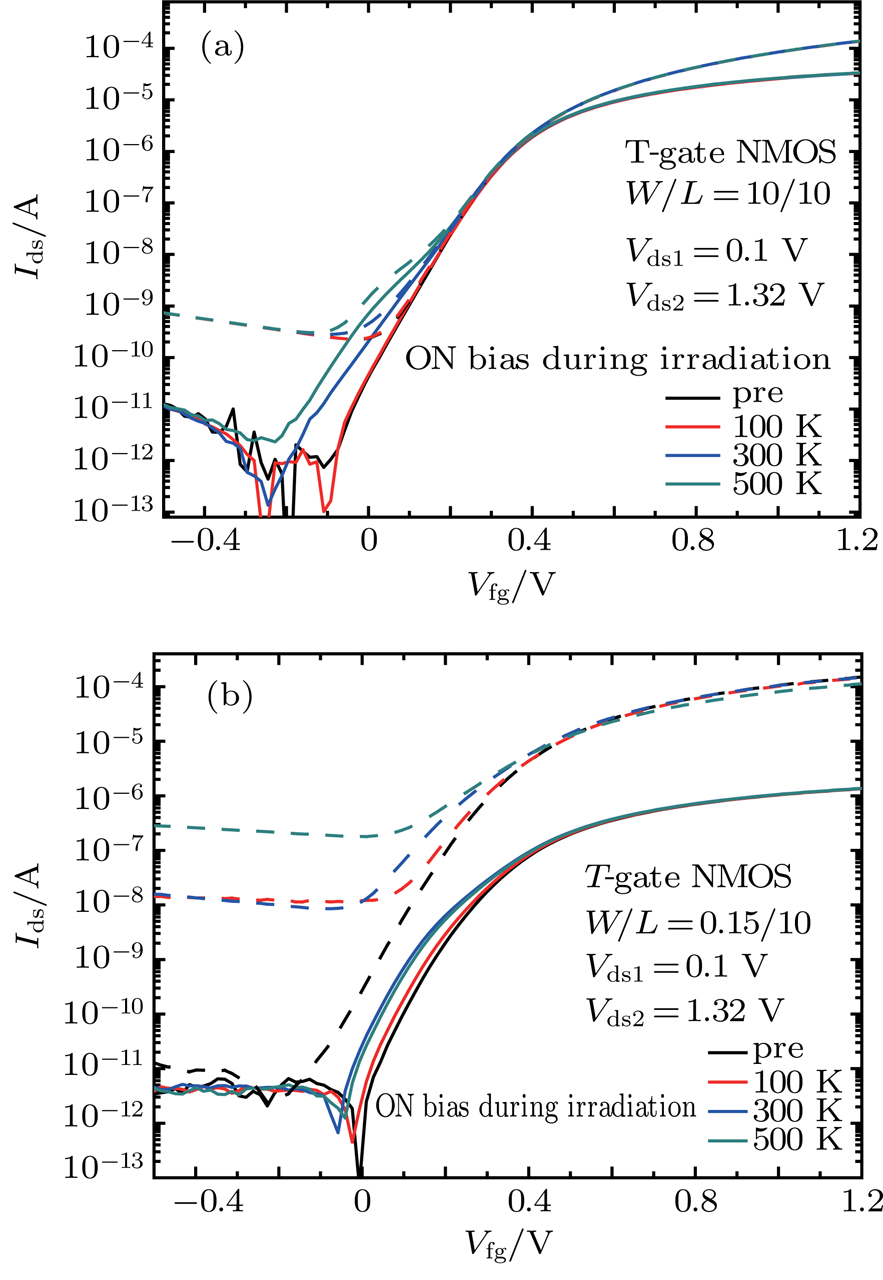

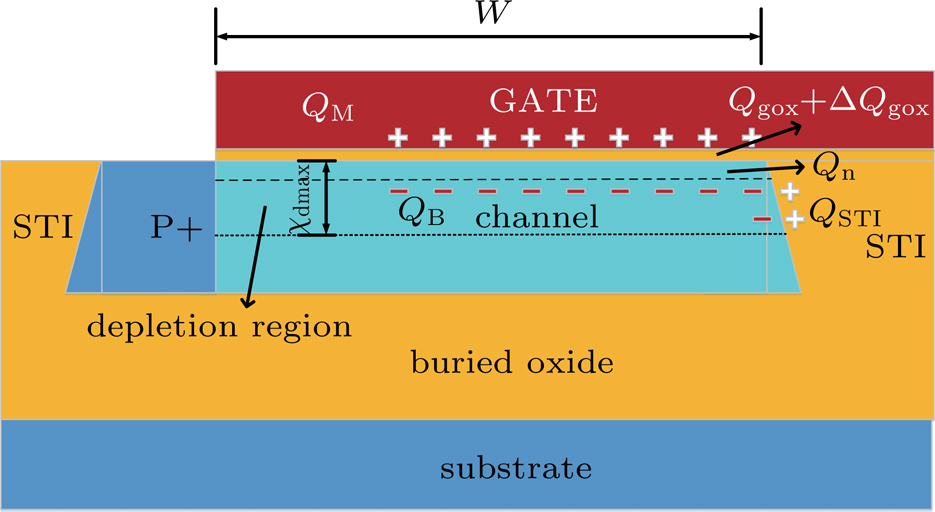

Figure

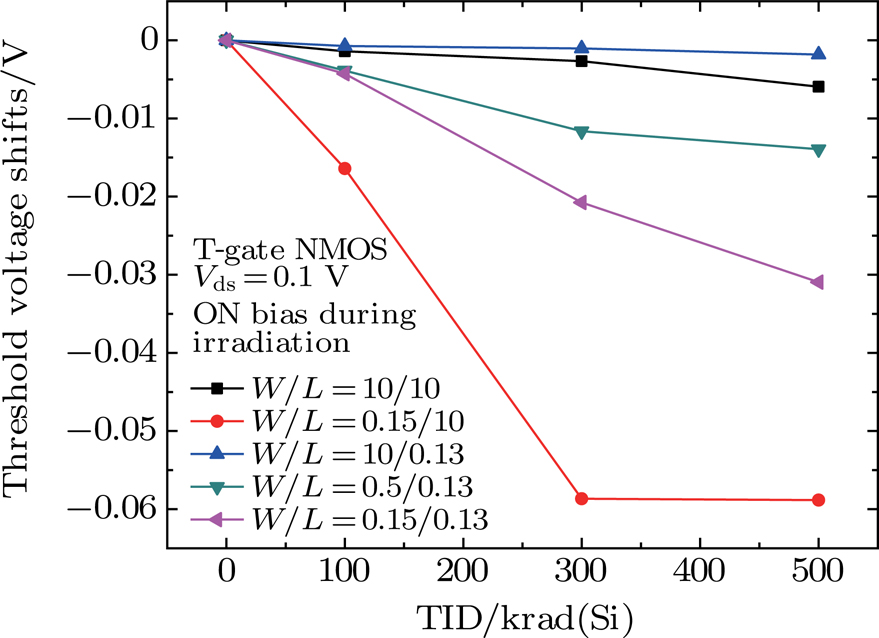

The threshold voltage

| Fig. 3. (color online) Threshold voltage shifts of front gate transistors versus the TID for PDSOI nMOSFETs with different channel sizes. |

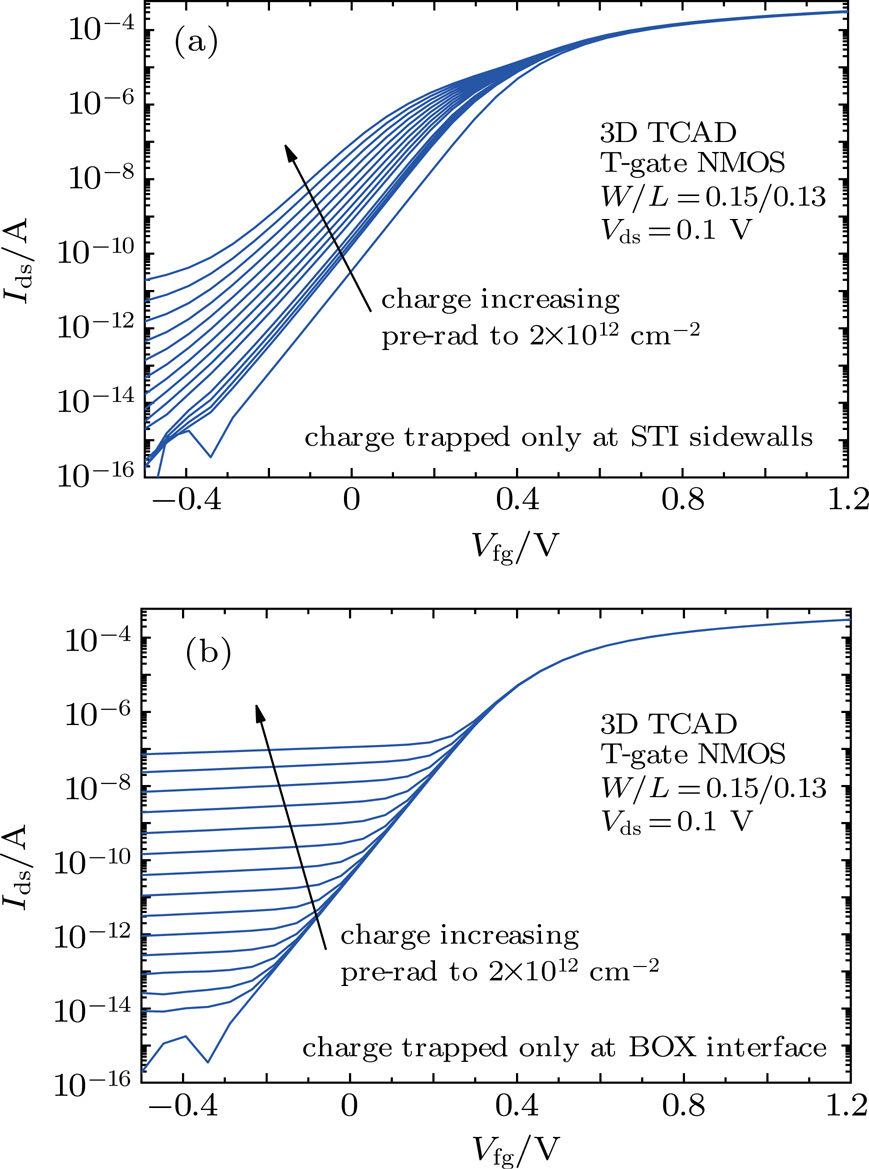

As stated above, both the buried oxide and the STI oxide can potentially affect the TID responses of SOI transistors. To distinguish the degradations between the BOX-related case and the STI-related case after radiation, 3D TCAD device simulations are performed using Sentaurus’s Sprocess and Sdevice. The process parameters are provided by the foundry. The simulation models used include conventional drift-diffusion model, the bandgap narrowing model for carrier transport; the Shockley–Read–Hall model, band-to-band tunneling model, and avalanche generation model for generation-recombination; doping-dependent mobility degradation, high-field saturation, degradation at interfaces for mobility. Assume that the uniform effective sheet charge density is placed along the STI sidewall and the top silicon/BOX interface for post-radiation simulation, meanwhile ignoring any possible interface trap generation.

Figure

| Fig. 5. (color online) Simulated pre-radiation, charge trapped (a) only at the silicon/STI interface and (b) only at the silicon/BOX interface for W/L = 0.15/0.13. |

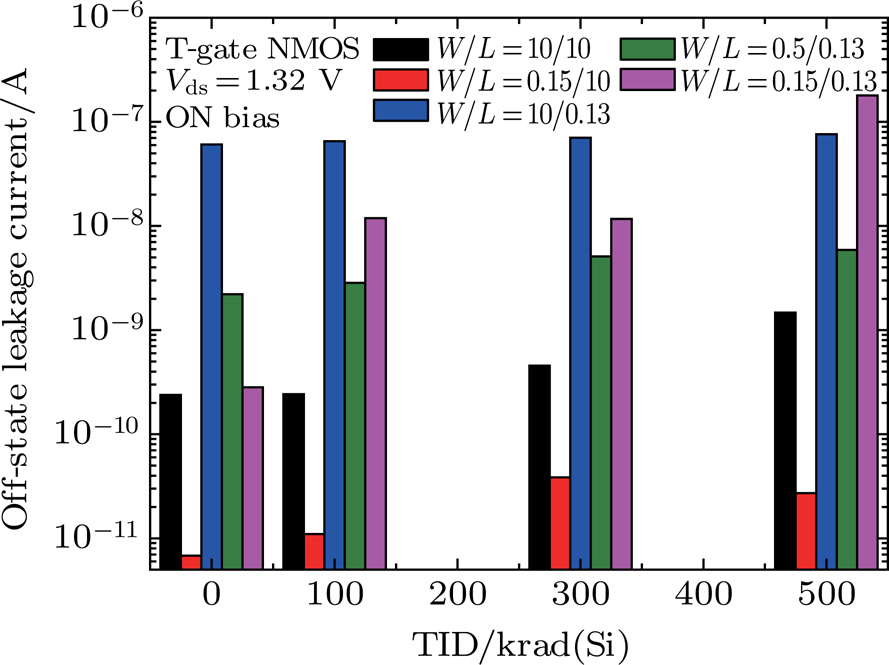

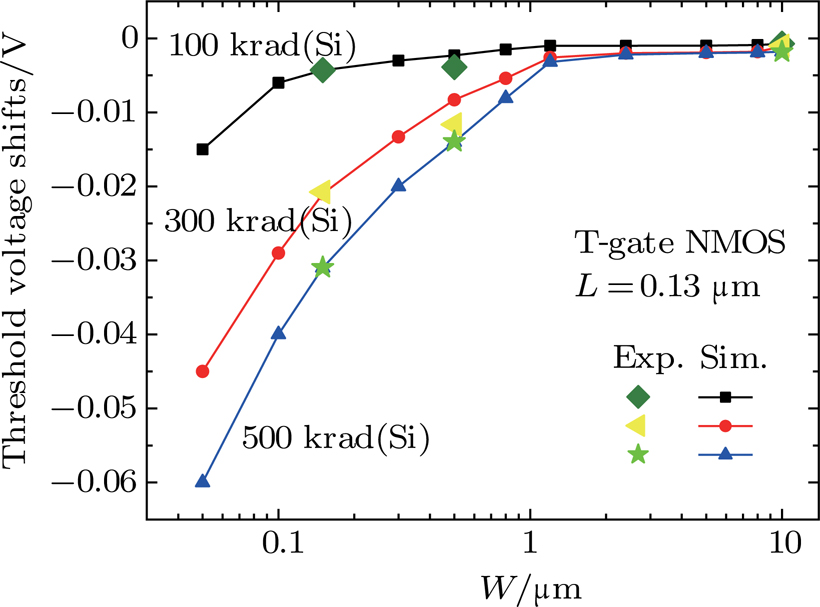

An additional insight into the TID sensitivities of such transistors related to their geometries,

The influence of channel width on TID response has been reported in bulk technology.[6–10] Most of the positive charges emerging during irradiation, which have escaped from the initial recombination, may be quickly trapped in the STI oxide along the conduction channel. The accumulation of positive charge eventually builds up a sufficient electric field to turn on an inversion channel where source–drain leakage current flows. For the narrow device, the accumulated positive charges at the STI edge not only determine the accumulation, depletion or inversion condition of the STI parasitic transistor (shown in Fig.

The RINCE for PDSOI NMOS can be explained by the charge sharing model as shown in Fig.

|

|

The positive charges induced by irradiation are trapped in the gate oxide (

|

|

|

|

|

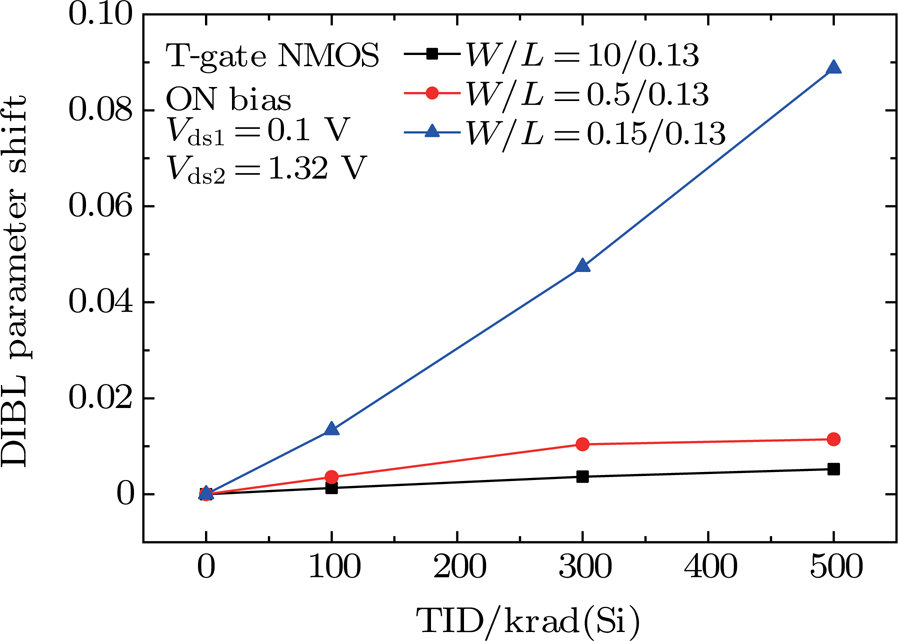

The DIBL effect on the drain current of a short channel is well known. High drain-voltage-induced barrier lowering between source and channel causes reinforced electron injection, leading to the leakage current increasing. Radiation-enhanced DIBL effect was firstly observed by Youk et al.[21] Many papers have been published for total dose radiation-enhanced DIBL effect which focused on the influence of short channel and irradiation bias conditions. With the channel width decreasing, radiation-induced charges trapped in the STI oxide will lead to RINCE, which further increases the off-state leakage current affecting the DIBL effect. Now, we investigate the influence of channel width on DIBL effect under total ionizing dose effect. The DIBL effect parameter is defined as

|

|

| Fig. 8. (color online) DIBL parameter shifts versus total dose for different transistor sizes under ON bias irradiation. |

This phenomenon may be explained by the following mechanisms. Radiation-induced positive charges trapped in the STI oxide and the buried oxide can both enhance the potential of the body, and the potential has a more significant change with high drain bias for the short channel device after irradiation. Then the lowering potential barrier at source causes the source injection to be enhanced, thus the enhanced DIBL effect is observed. However, the DIBL parameter for W/L = 10/0.13 device barely shifts. This indicates that the radiation-induced positive charges trapped in the buried oxide have almost no influence on the body potential. With the channel width narrowing, the influence of radiation-induced positive charges trapped in the STI oxide on the body potential become more obvious. Thus the radiation-enhanced body potential for the narrow device lowers the potential barrier at source, which furthermore causes the source injection to be enhanced. As a result, the enhanced DIBL effect occurs, which further degrades the device characteristics, such as the threshold voltage shift, the off-state leakage current increasing, the voltage gain decreasing, etc. Designers should take narrow devices into consideration when designing radiation-toleration ASICs.

An enhanced radiation-induced narrow channel effect (RINCE) in 0.13-

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] | |

| [20] | |

| [21] |