† Corresponding author. E-mail:

Gate-grounded N-channel MOSFET (GGNMOS) has been extensively used for on-chip electrostatic discharge (ESD) protection. However, the ESD performance of the conventional GGNMOS is significantly degraded by the current crowding effect. In this paper, an enhanced GGNMOS with P-base layer (PB-NMOS) are proposed to improve the ESD robustness in BCD process without the increase in layout area or additional layer. TCAD simulations are carried out to explain the underlying mechanisms of that utilizing the P-base layer can effectively restrain the current crowing effect in proposed devices. All devices are fabricated in a 0.5-

Gate-grounded N-channel MOS (GGNMOS) is widely used in electrostatic discharge (ESD) protection because of its active discharge mechanism and compatibility of bipolar-CMOS–DMOS (BCD) technologies.[1] However, as the technology advances, design of area efficient and robustness GGNMOS becomes extremely challenging, due to the lightly doped drain (LDD) existing in deep-submicron BCD technology aimed at overcoming the hot-carrier effect, which leads to significant current crowding and consequently degradation of GGNMOS device’s ESD robustness.[2] Several studies have been reported to improve the ESD robustness of GGNMOS, including the incorporation of substrate-triggering,[3] gate-coupled technologies,[4] drain/source silicide blocking,[5,6] and P-ESD implantation.[7–9] Among them, the approaches of substrate-triggering and gate-coupled technologies are realized by introducing additional resistors for triggering-assist, which will consume more layout area and cost. Likewise, the approach of drain/source silicide blocking will increase drain contact-to-gate space (DCGS) and source contact-to-gate space (SCGS), which will also consume more layout area and cost. Unlike, the approach of adding the P-ESD implantation layer in the GGNMOS is attractive as it can introduce an extra vertical current path during the ESD event,[7–9] without increasing layout area. Nevertheless, this method will induce a sharp increase in leakage current.[10] Furthermore, ESD implantation is not a standard step in BCD process, thus resulting in an increase in fabrication cost and complexity.

To improve the ESD characteristics without increase in layout area and fabrication cost, an enhanced GGNMOS by using P-base layer (PB-NMOS) are proposed in this work. As the base region of bipolar transistor, P-base layer is an inherent layer in BCD process.[11] And thus, no extra step and/or cost will incur in proposed PB-NMOS. Three types of PB-NMOS will be designed and fabricated in 0.5-

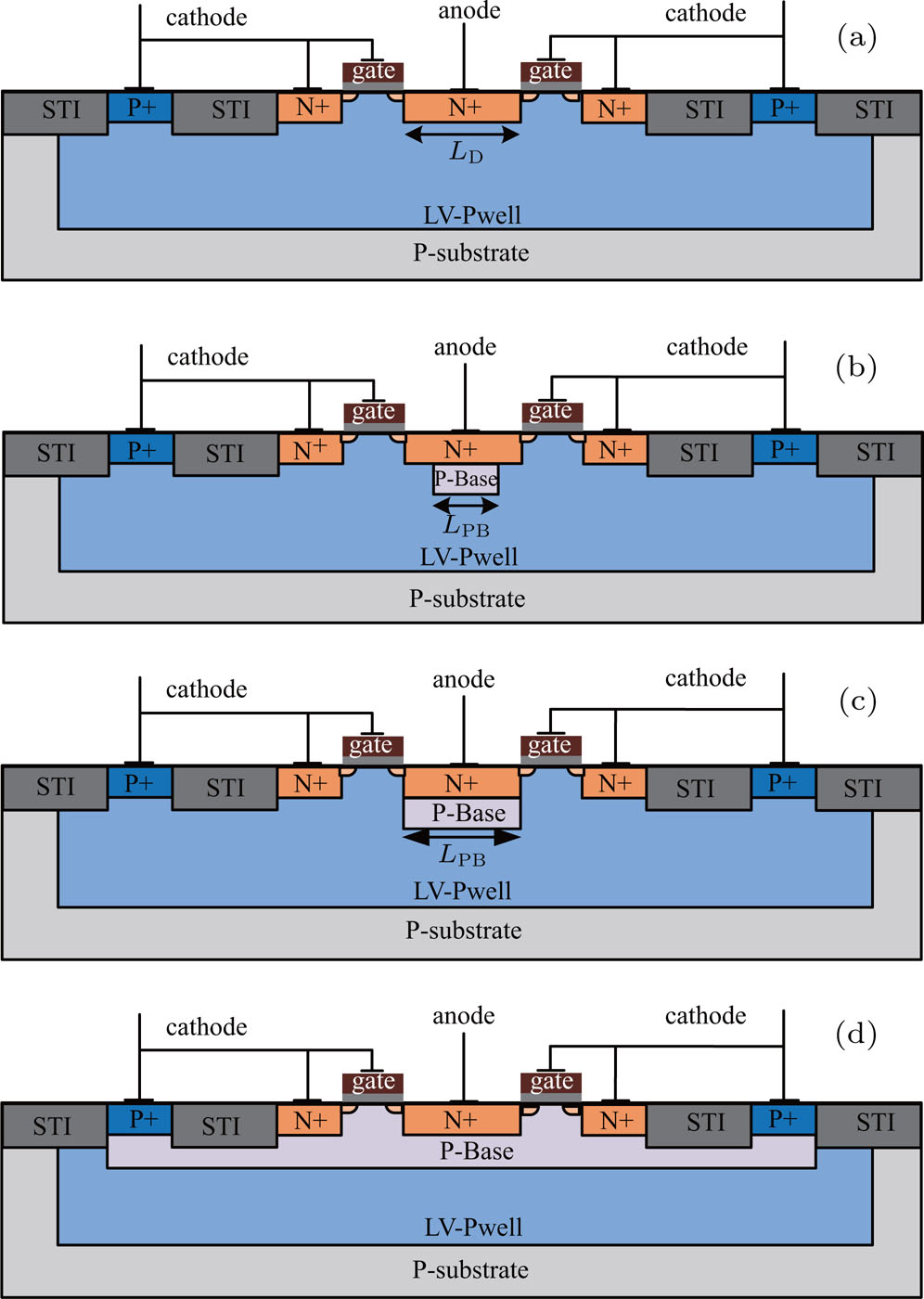

The cross-sectional view of conventional GGNMOS is shown in Fig.

| Fig. 1. Cross-sectional views of (a) conventional GGNMOS, (b) proposed PB-NMOS_type1, (c) proposed PB-NMOS_type2, and (d) proposed PB-NMOS_type3. |

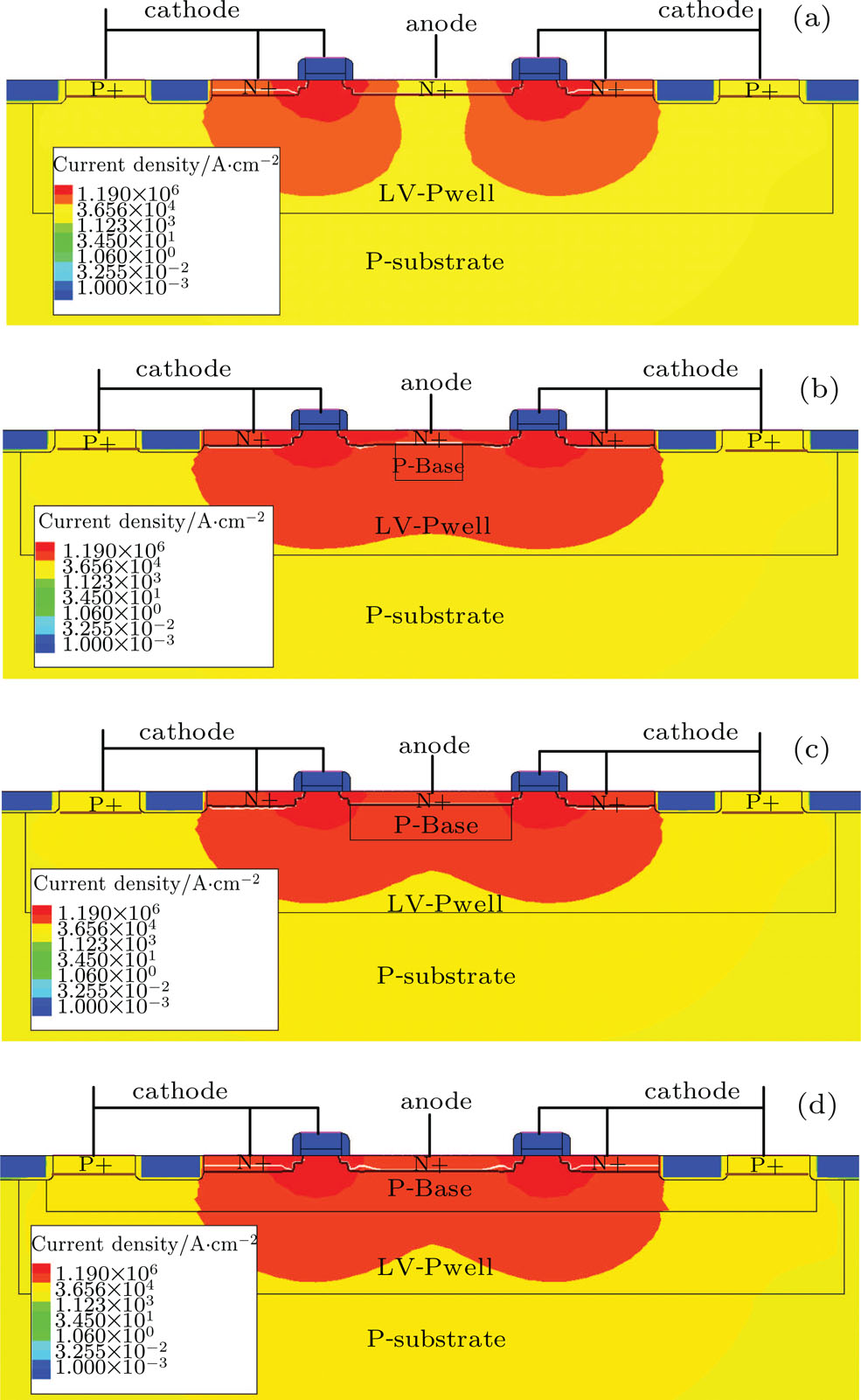

In order to further explore the physics mechanisms of the GGNMOS and proposed PB-NMOS, two-dimensional (2D) Technology Computer-Aided Design (TCAD) simulation has been carried out by Sentaurus tool,and all the layers and dimensions are set according to the design rules of a real 0.5-

| Fig. 2. TCAD simulation results of the current density distributions in (a) conventional GGNMOS, (b) proposed PB-NMOS_type1, (c) proposed PB-NMOS_type2, and (d) proposed PB-NMOS_type3. |

However, the current crowding effect is effectively alleviated in proposed PB-NMOS_type1 due to the imbedded P-base layer which induces an additional vertical NPN current path, as shown in Fig.

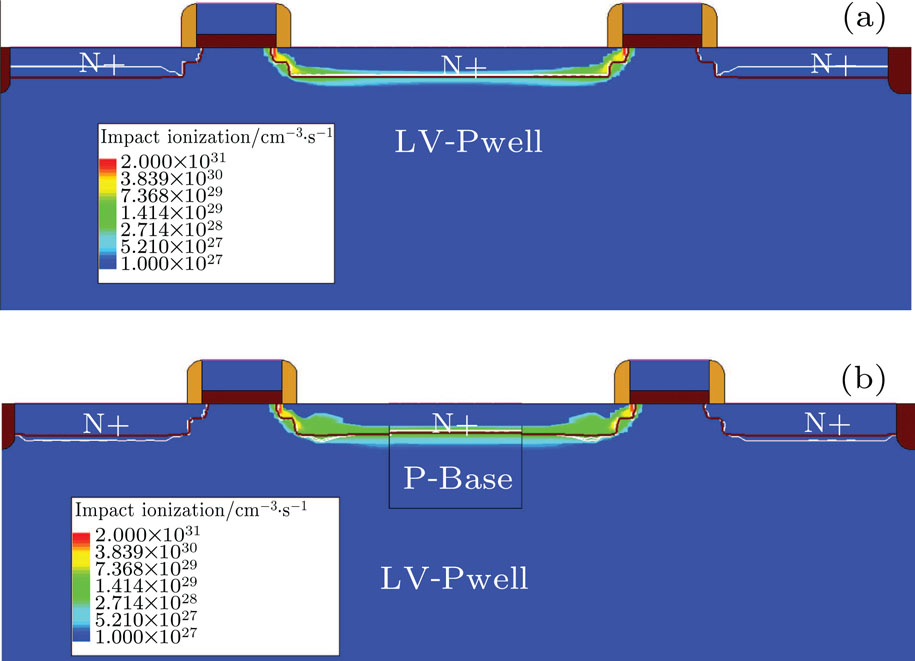

Furthermore, in order to prove the benefits of additional vertical current path in proposed PB-NMOS devices, the impact ionization distributions of conventional GGNMOS and proposed PB-NMOS_type1 are simulated and shown in Figs.

All the conventional GGNMOS and proposed PB-NMOS devices are fabricated in a 0.5-

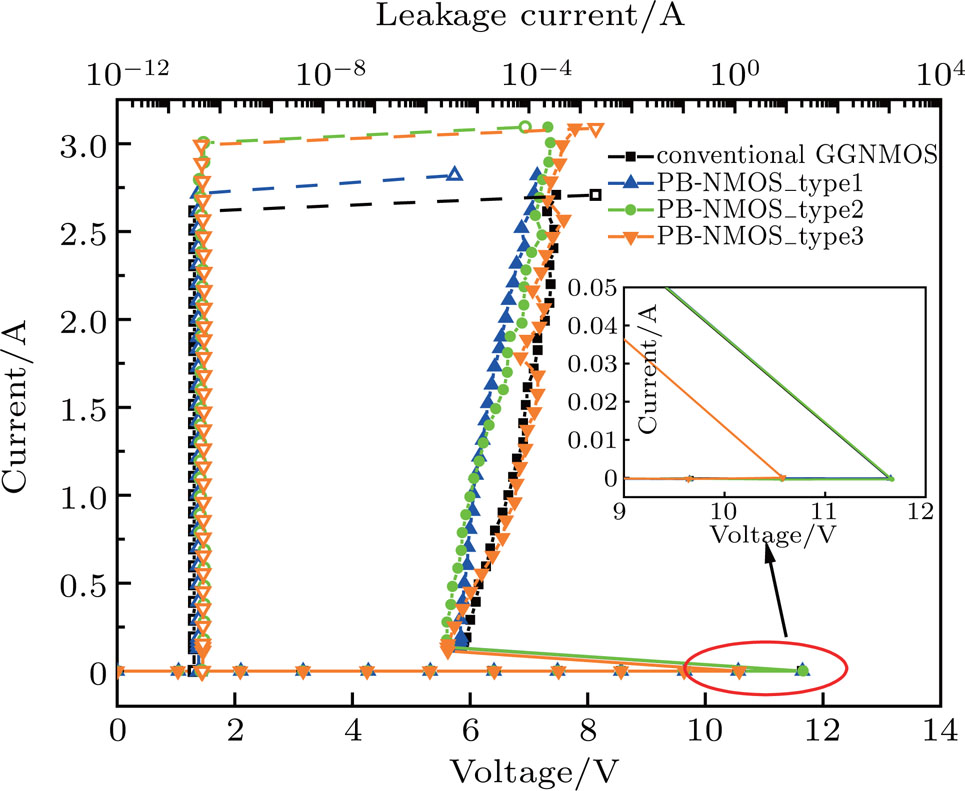

The measured TLP I–V curves of the conventional GGNMOS and proposed PB-NMOS devices are illustrated in Fig.

| Table 1.

Electrical characteristics of the proposed structures and the conventional GGNMOS according to design variable. . |

However, such a surrounding P-base region in PB-NMOS_type3 can reduce the trigger voltage (Vt1) of proposed PB-NMOS_type3, as listed in Table

Leakage current is another critical design metric for the ESD devices. It can be seen that all proposed PB-NMOS devices have approximately the same leakage currents as the conventional GGNMOS, which is an effective improvement of leakage current compared to the GGNMOS with P-ESD implantation.[10] As shown in Fig.

From the above discussion, all the proposed PB-NMOS devices are superior to the conventional GGNMOS in ESD robustness. Particularly, PB-NMOS_type3 has the best ESD robustness due to the enhanced ESD characteristics on relatively higher failure current, smaller trigger voltage, and smaller snapback region.

An enhanced GGNMOS by using the P-base layer called PB-NMOS, has been developed and verified in a 0.5-

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] |