High-performance synaptic transistors for neuromorphic computing

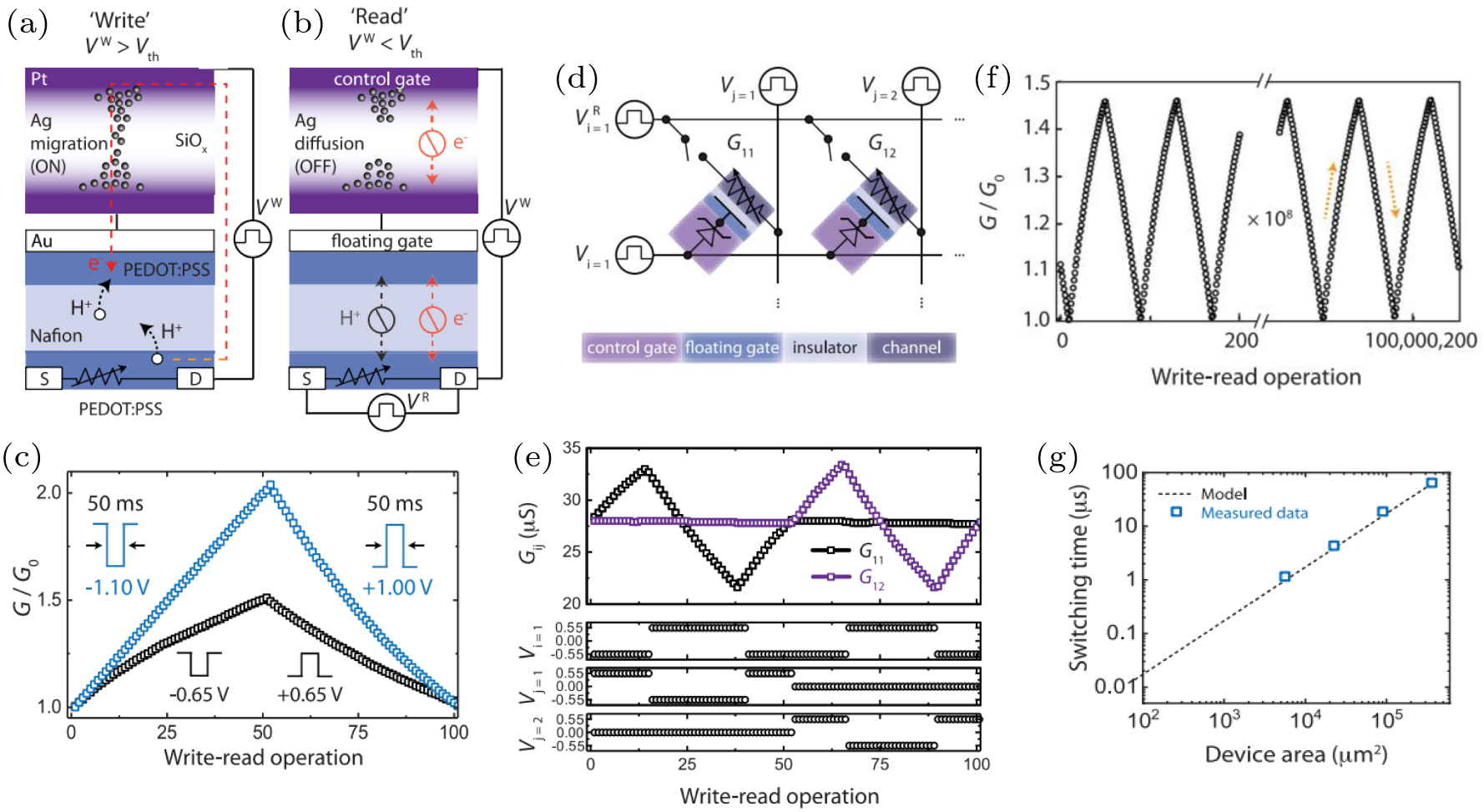

(a) The “write” and (b) “read” states of an IFG cell consisting of a CBM and a redox transistor. (c) Programming of an IFG cell at two different write voltages. (d) Schematic of a 1-by-2 IFG resistive memory array. (e) Selective addressing by subjecting