Investigation of gate oxide traps effect on NAND flash memory by TCAD simulation

Project supported by the SanDisk Info Tech Shanghai, China and the Institute of Microelectronic Materials & Technology, School of Materials Science and Engineering, Shanghai Jiao Tong University, China.

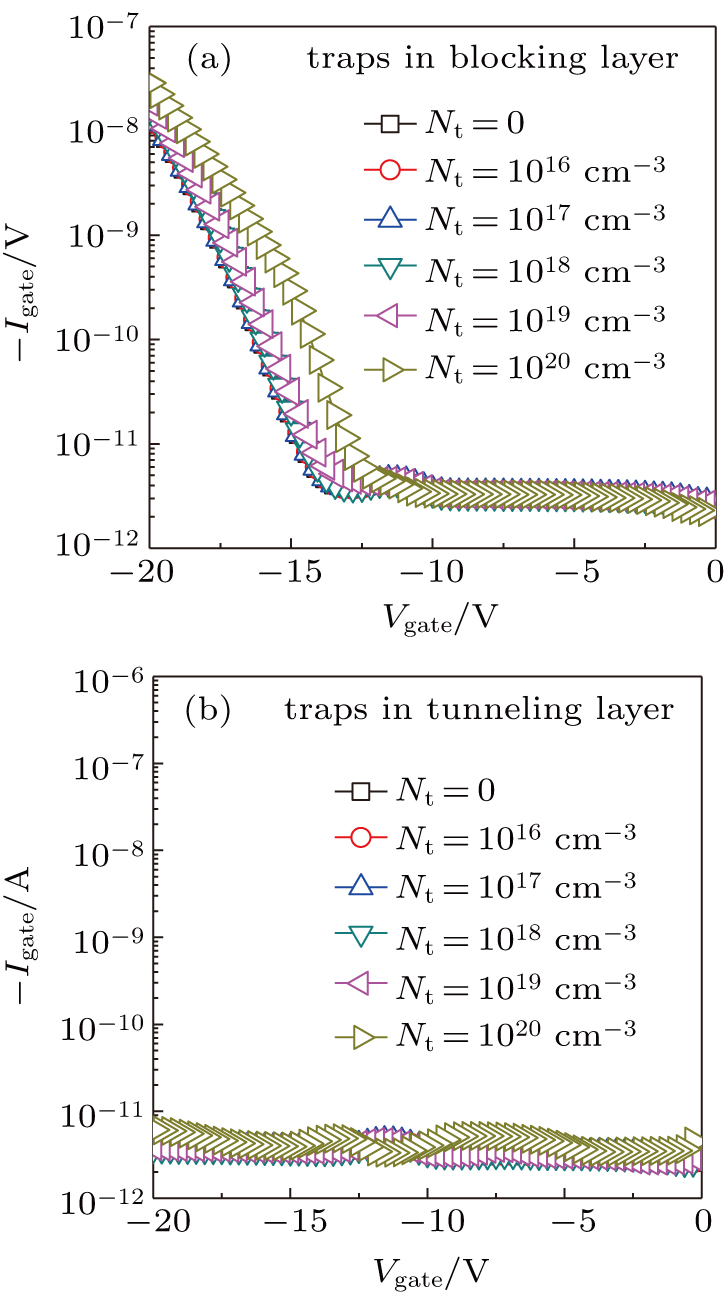

Gate leakage currents varying with gate bias under different trap conditions in erase process: (a) different trap densities in blocking layer at 2 eV and (b) different trap densities in tunneling layer at 2 eV.