† Corresponding author. E-mail:

Project supported by the National Key Research and Development Project, China (Grant No. 2017YFB0503200), the National Natural Science Foundation of China (Grant Nos. 61434005, 61474118, 11774343, and 11674314), the Science and Technology Program of Jilin Province, China (Grant No. 20160203013GX), and the Youth Innovation Promotion Association, China (Grant No. 2017260).

We establish a novel method of controlling the transverse modes of vertical cavity surface emitting lasers (VCSELs) to achieve 1 mW single-fundamental-mode lasing. A dielectric mode filter is installed on top of the VCSEL. The dielectric layer (SiO2) is deposited and patterned to modify the mirror reflectivity across the oxide aperture via antiphase reflections. This mode selection is nondestructive and universally applicable for other structures under single transverse mode. Destructive etching techniques (dry/wet) or epitaxial regrowth are also not required. This method simplifies the preparation process and improves the repeatability of the device. Measurements show that under continuous-wave current injection, the side-mode suppression ratio exceeds 30 dB.

Vertical cavity surface emitting lasers (VCSELs) are effective solutions to end users’ requirements for engineering applications because of their low power consumption, narrow bandwidth, high speed, polarization stability, and single mode in cloud services, internet protocol television, optical storage, gas sensing, and atomic chip devices.[1–4] Single-mode and high-power items are important in optical systems. The number of transverse modes rises dramatically as lateral dimensions increased. Thus the balance between maintaining single mode and increasing output power is a key research content. Several different solutions have been proposed to achieve single-mode high-power devices, which include weakening lateral cladding with a photonic crystal structure,[5,6] the high-order-mode loss with a triangular hole structure,[7] anti-resonant reflecting optical waveguide structure,[8] metal windows,[9] impurity-induced disordering of DBRs,[10] buried tunnel junctions,[11] and surface relief structure.[12–15] The highest output power of 7.5 mW at a side-mode suppression ratio (SMSR) of approximately 40 dB is demonstrated via triangular hole structure.[7] A single mode power of above 6 mW with SMSR higher than 30 dB is reported at 850 nm.[14]

However, these methods have disadvantages, such as complex epitaxial growth or device processing. Furthermore, the control precision of etching depth or epitaxial regrowth affects the reproducibility and yield of devices. In this study, a novel type of VCSEL with a dielectric mode filter is developed, and its performance is investigated. The new method for mode selection does not require additional lithography or semiconductor etching. The deposition of a dielectric material (SiO2 layer) on top of the surface results in current insulation and mode filter through one self-aligned photoresist process and etching. Then we can create spatially dependent out-of-phase without semiconductor etching or regrowth, thereby suppressing the higher-order mode and preserving the fundamental mode.

We deposit a single λ/4-thick dielectric material (SiO2 layer) to maximize the out-of-phase reflection on the surface of VCSEL. The SiO2 layer is deposited over the entire top surface of the top GaAs current-spreading layer to maximize threshold modal gain for all transverse modes, as shown in Fig.

| Fig. 1. (color online) Calculated VCSEL threshold gain with (red line) and without (blue line) SiO2 layer. |

A transfer matrix based method is used to calculate the threshold modal gain, and the optimum single-mode region is designed for the mode discriminator that minimizes the threshold modal gain in the center of the device and maximizes in high-order-mode regions. By calculating different patterns distribution along the radius direction, LP11 and LP21 are the main factors that affect single mode operation (LP01). Thus we focus on the distribution of the three modes (LP01, LP11, and LP21). The mesa diameter and oxidation aperture in the simulation are 20 and 6 μm, respectively. The mesa center is the origin of the coordinates, and the distribution of three patterns (LP01, LP11, and LP21) along the radius direction is observed in Fig.

| Fig. 2. (color online) The distribution of three patterns (LP01, LP11, and LP21) along radius direction. |

This method creates a circular annulus with a depth of μ/4 and an inner diameter of 3 μm, which is etched into the center of the VCSEL. The deposited SiO2 layer–GaAs and SiO2 layer–air interfaces are out of phase with respect to the reflections from the DBR interfaces. The mirror loss increases further and the higher-order modes are suppressed. The SiO2 layer in the central region is etched to make the fundamental mode lase and suppress the higher-order modes.

A schematic representation of the VCSEL structure is shown in Fig.

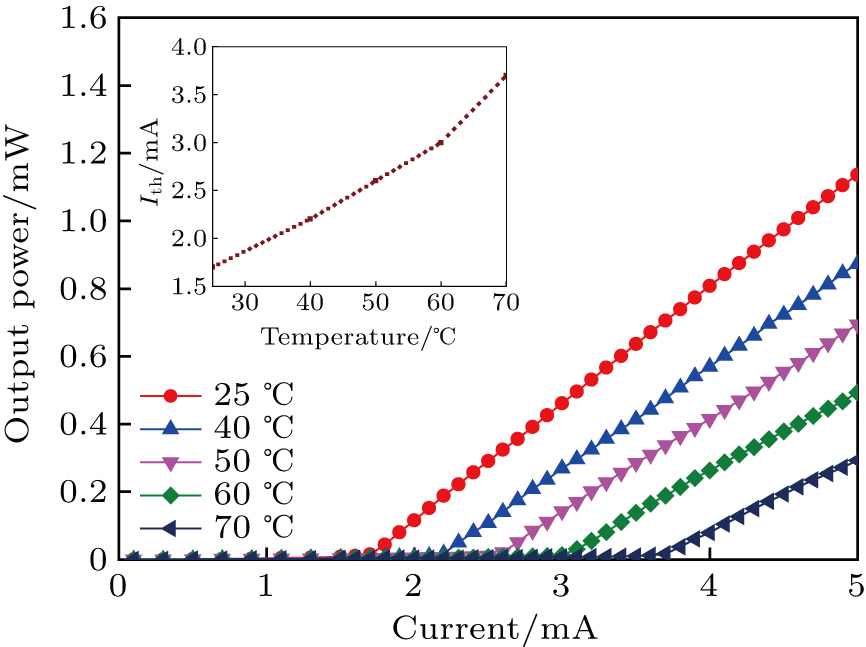

Lasing characteristics are measured under continuous-wave current injection at room temperature. Figure

| Fig. 4. (color online) L–I–V characteristics and the variation of threshold current (the inset) of the continuous-wave current injection for the VCSEL with a dielectric mode filter. |

The samples with mode filter and without mode filter are compared, as shown in Fig.

Figure

| Fig. 6. (color online) Spectra of the VCSEL with a dielectric mode filter. The fabricated device is tested under I = 4 mA. |

The measured near field patterns at different continuous-wave currents (I = 2, 3, and 4 mA) are shown in Fig.

We fabricate and measure VCSEL with a dielectric mode filter, which demonstrates a stable single mode performance. Measurements reveal that at continuous-wave current injection, the single-mode output power is 1 mW with the SMSR exceeding 30 dB throughout the current operating range (below 5 mA). The dielectric mode filter modifies the optical properties via antiphase reflections. Meanwhile, the method for the simple deposition and patterning of a single SiO2 layer is deemed appropriate for VCSELs of any wavelength. Unlike other single-mode techniques, the proposed method could make device adjustment biased due to the thickness of the SiO2 layer. Furthermore, the size of the pattern could be adjusted at any time via process variability. The dielectric mode filter could be patterned using a simple self-aligned photoresist process/etching process to improve reproducibility and yield in future single-mode technologies.

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] |