Near-interface oxide traps in 4H–SiC MOS structures fabricated with and without annealing in NO

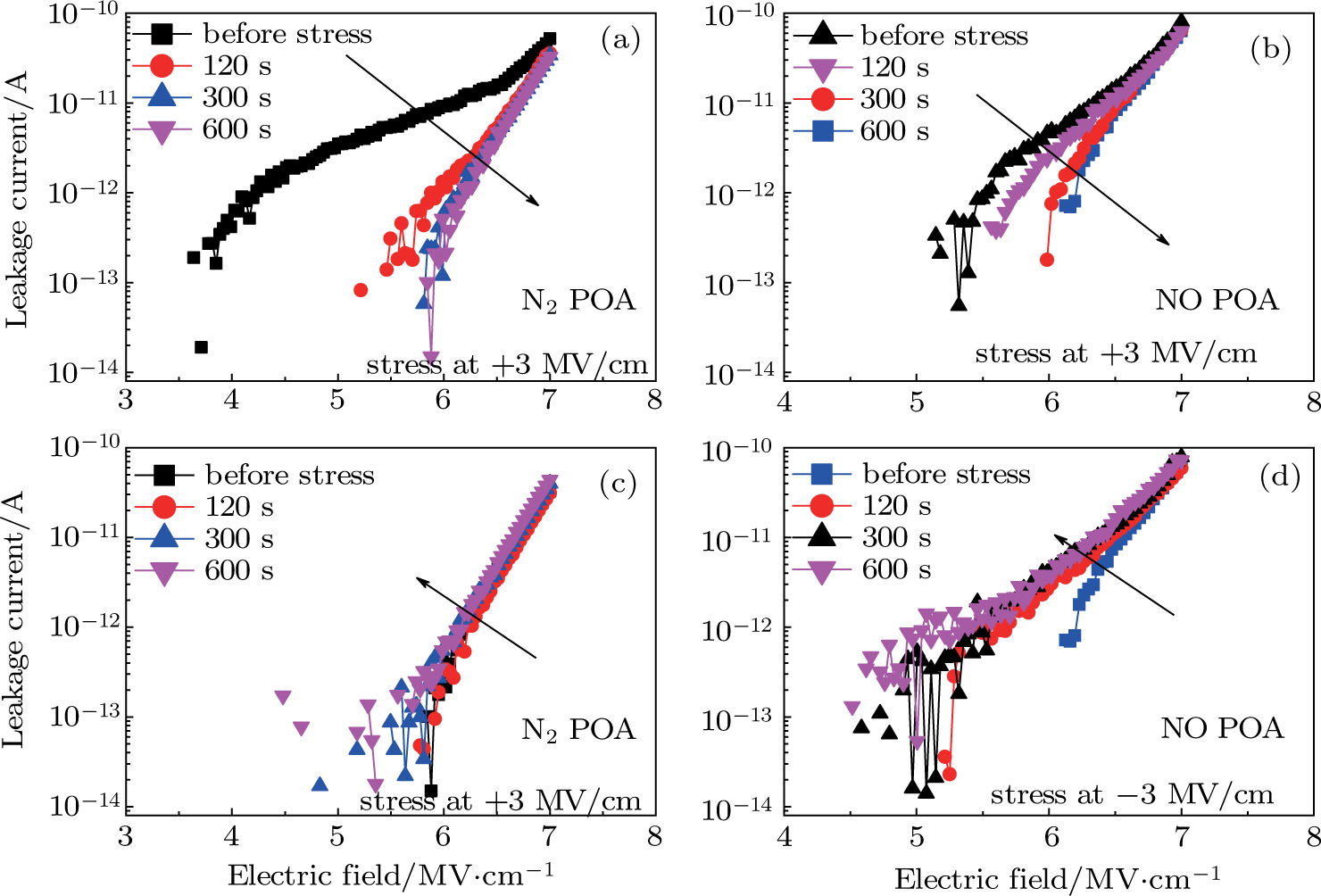

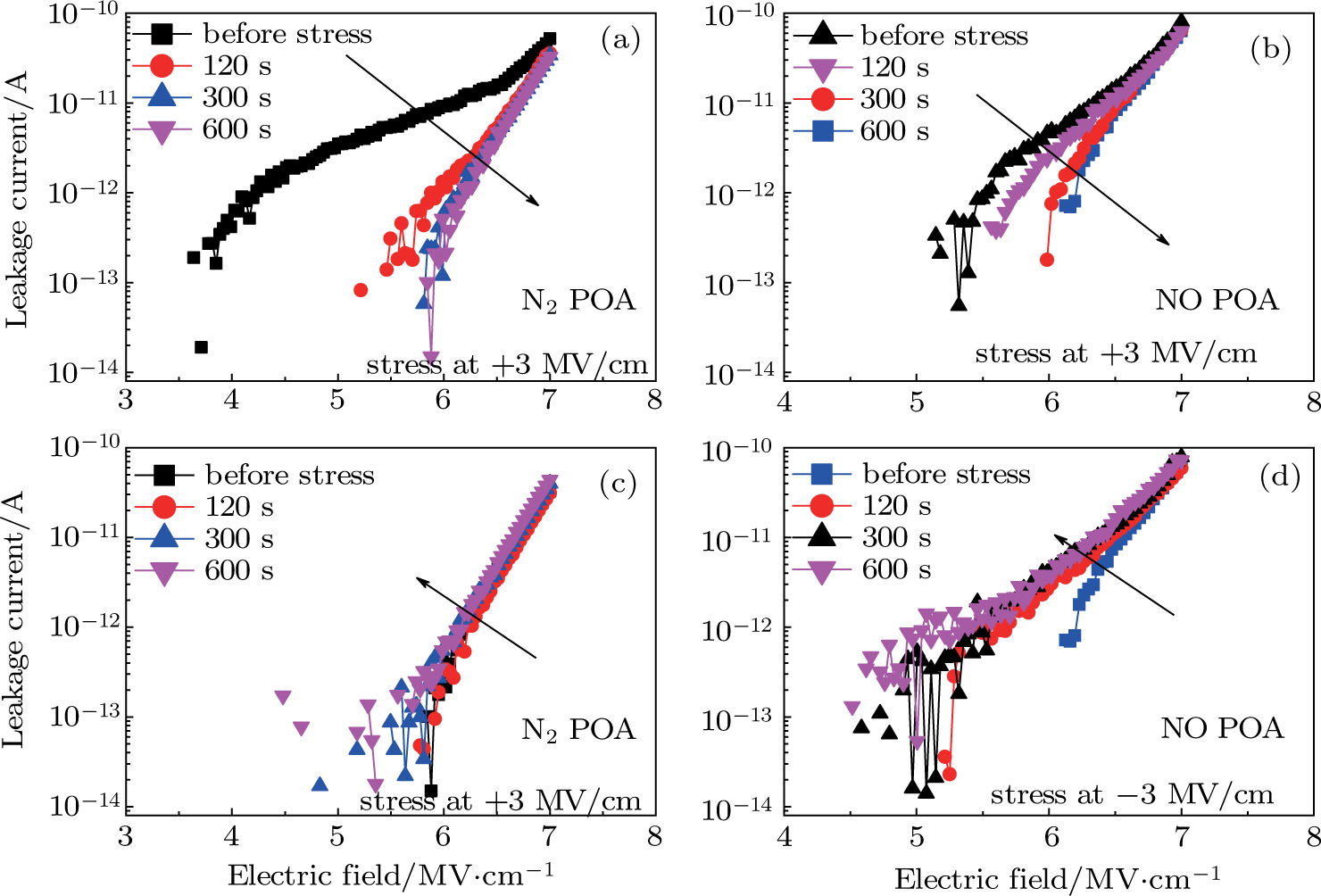

(color online) Typical leakage-electric field curves of the N2 POA sample and NO POA sample with different stress times.

Near-interface oxide traps in 4H–SiC MOS structures fabricated with and without annealing in NO |

|

(color online) Typical leakage-electric field curves of the N2 POA sample and NO POA sample with different stress times. |

|