Near-interface oxide traps in 4H–SiC MOS structures fabricated with and without annealing in NO

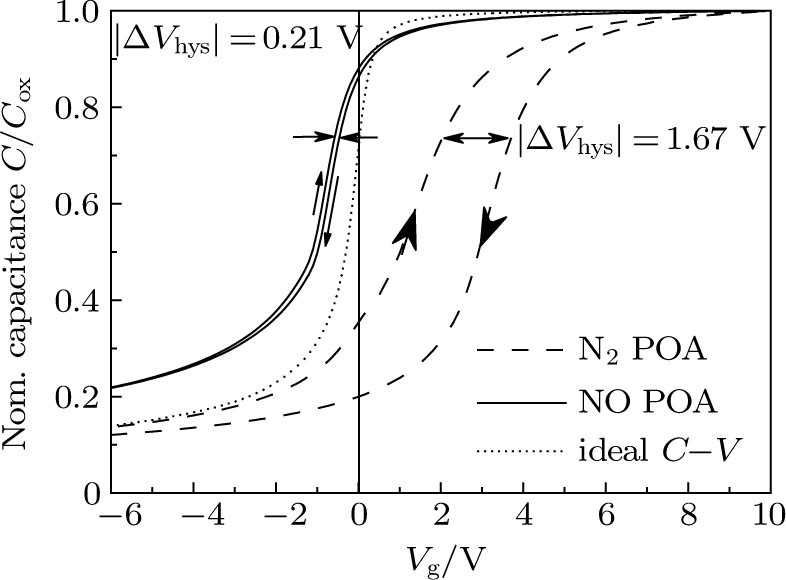

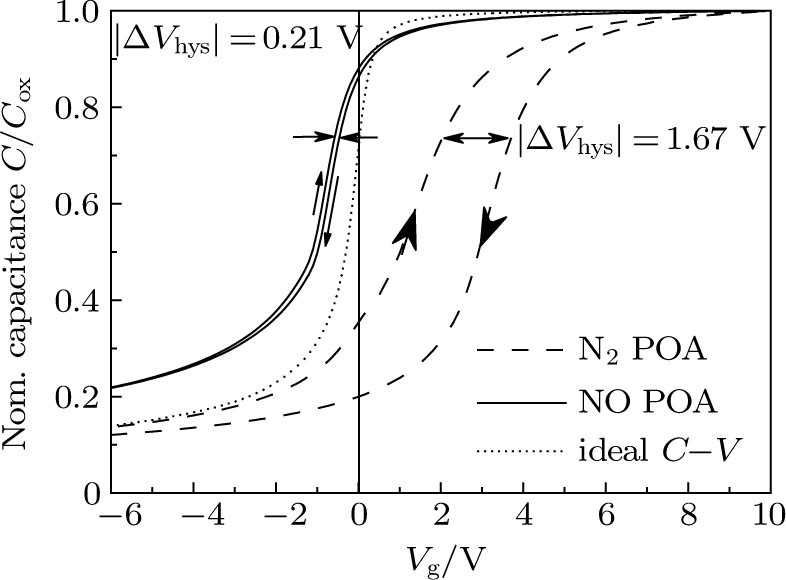

Hysteresis C–V curves of the SiC MOS capacitors at 100 kHz for N2 and NO POA samples, respectively.

Near-interface oxide traps in 4H–SiC MOS structures fabricated with and without annealing in NO |

|

Hysteresis C–V curves of the SiC MOS capacitors at 100 kHz for N2 and NO POA samples, respectively. |

|