Horizontal InAs nanowire transistors grown on patterned silicon-on-insulator substrate

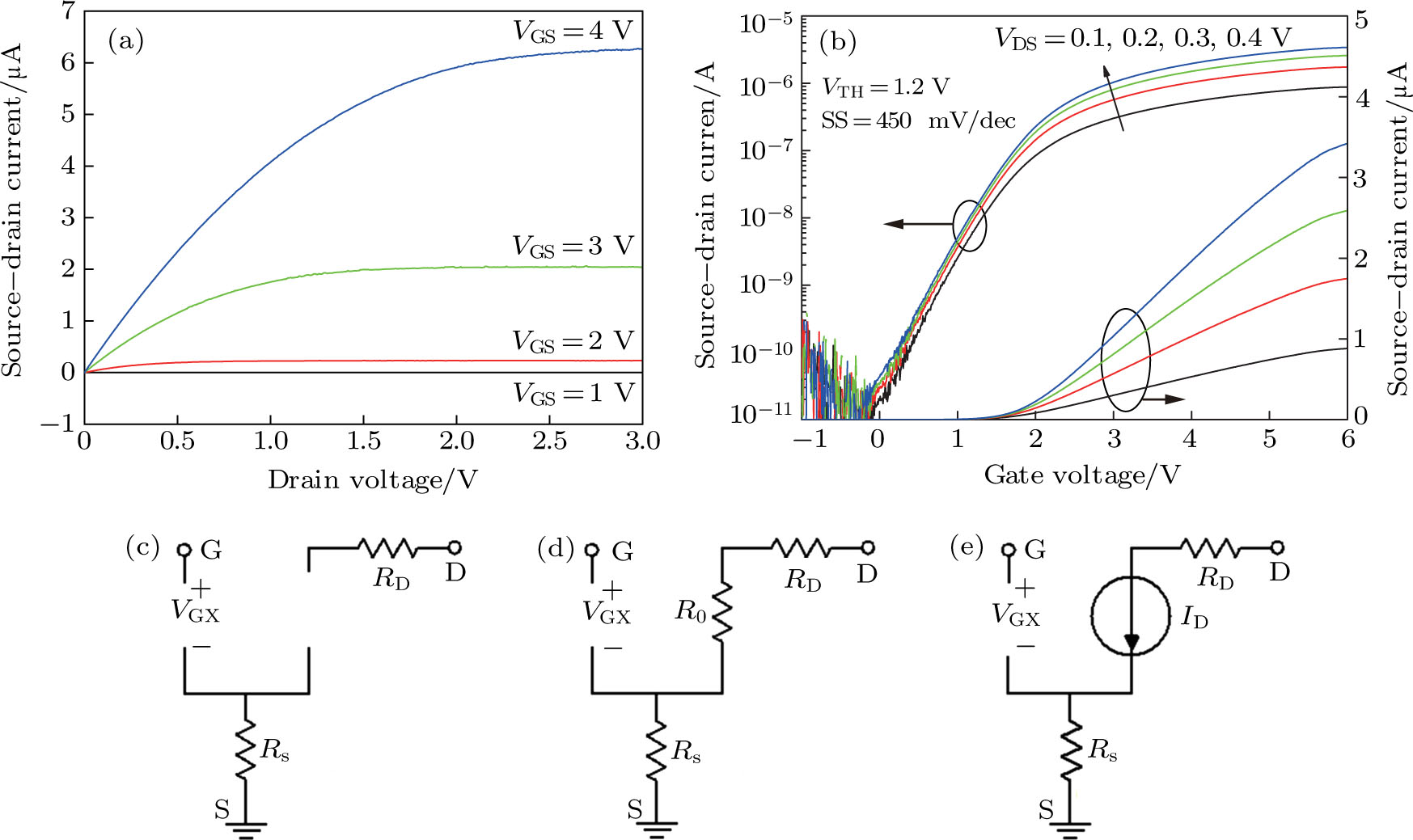

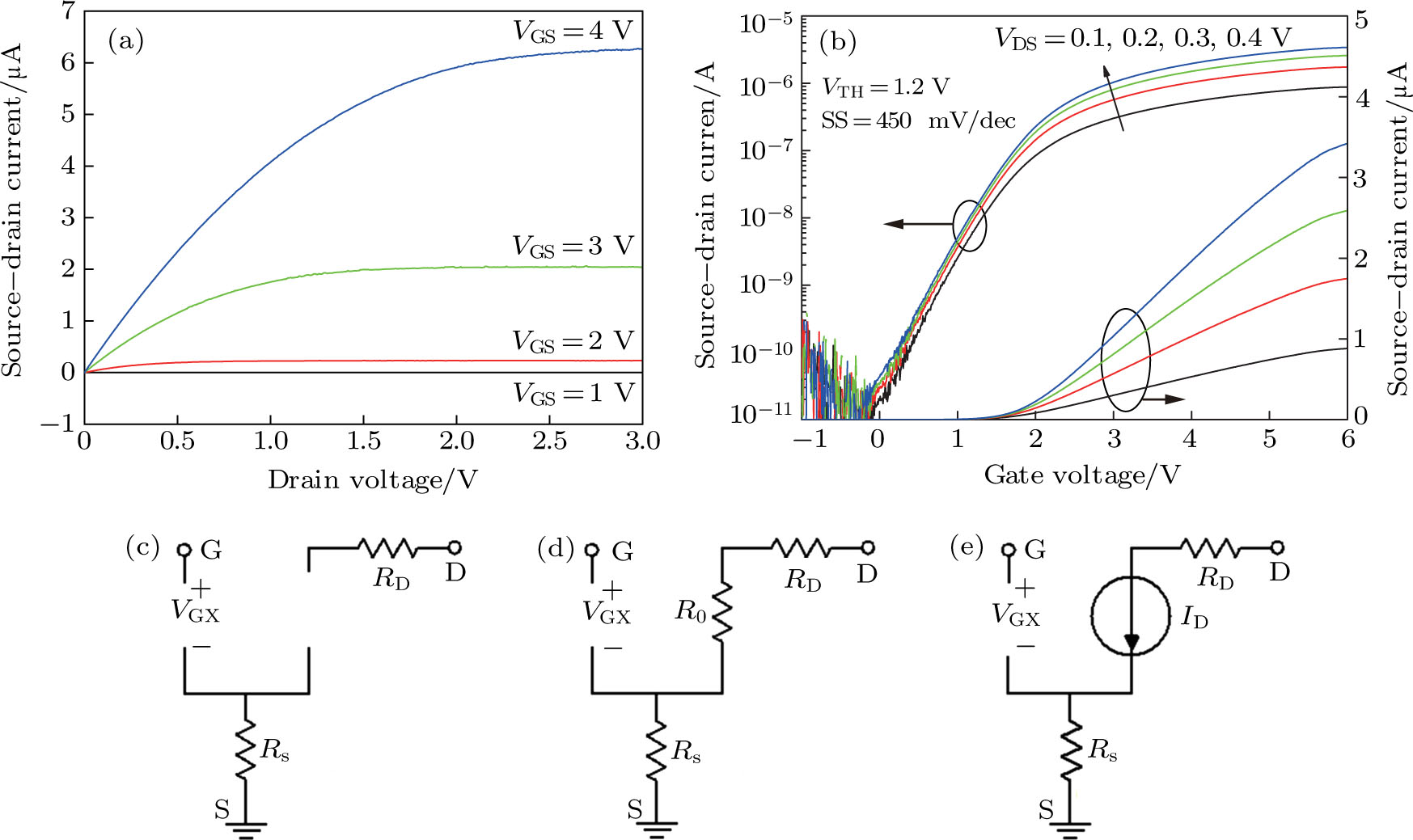

(color online) Room-temperature electrical performances. (a) Output curves with

Horizontal InAs nanowire transistors grown on patterned silicon-on-insulator substrate |

|

(color online) Room-temperature electrical performances. (a) Output curves with |

|