Equivalent distributed capacitance model of oxide traps on frequency dispersion of

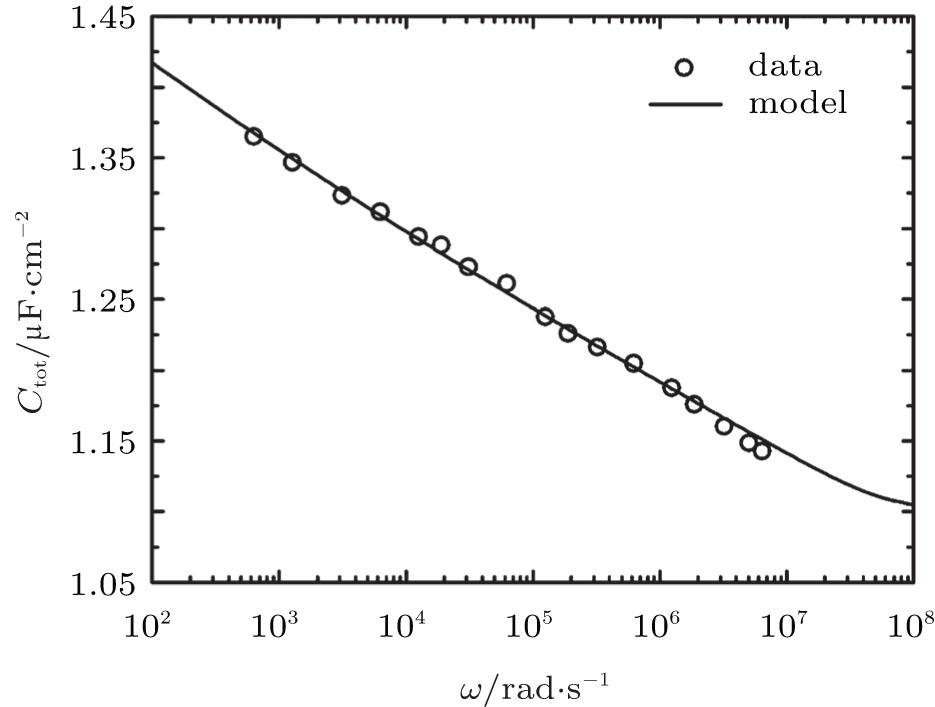

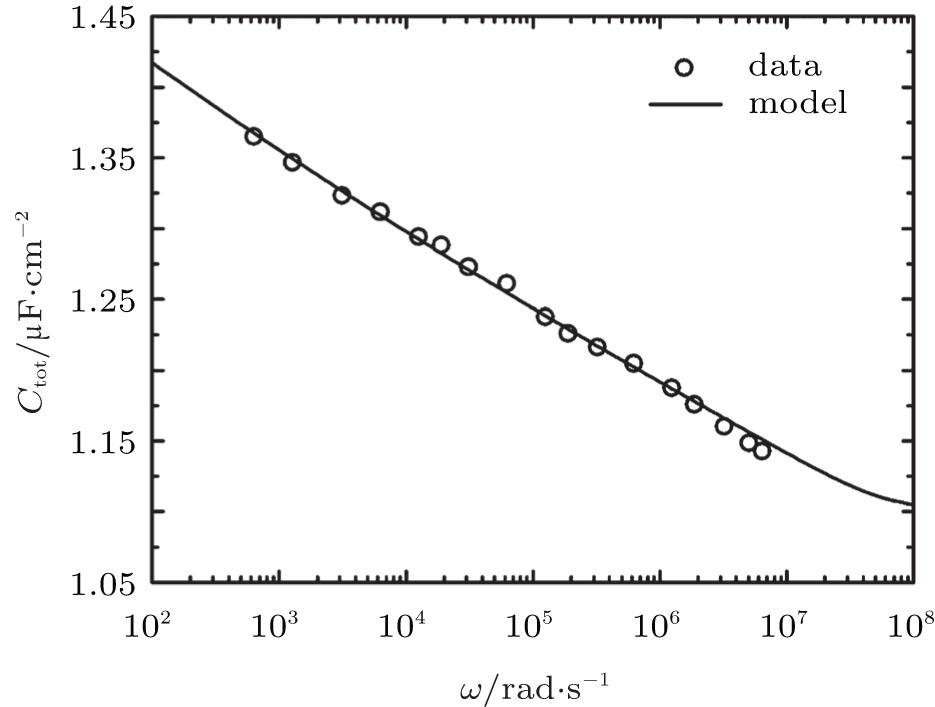

Comparison between simulated results (solid line) and experimental data (open circles) for a Pd/4.5-nm Al2O3/p-InGaAs MOS device with the gate biased at −1.8 V.

Equivalent distributed capacitance model of oxide traps on frequency dispersion of |

Comparison between simulated results (solid line) and experimental data (open circles) for a Pd/4.5-nm Al2O3/p-InGaAs MOS device with the gate biased at −1.8 V. |

|