† Corresponding author. E-mail:

Project supported by the National Natural Science Foundation of China (Grant No. 61474085).

Tunnel field effect transistors (TFETs) are promising devices for low power applications. An analytical threshold voltage model, based on the channel surface potential and electric field obtained by solving the 2D Poisson’s equation, for strained silicon gate all around TFETs is proposed. The variation of the threshold voltage with device parameters, such as the strain (Ge mole fraction x), gate oxide thickness, gate oxide permittivity, and channel length has also been investigated. The threshold voltage model is extracted using the peak transconductance method and is verified by good agreement with the results obtained from the TCAD simulation.

Continuous scaling of traditional metal-oxide-sem-icon-ductor field-effect transistors (MOSFETs) for high performance can result in a rapid increase of power, which blocks its applications in the low power domains.[1–3] Therefore, tunnel field effect transistors (TFETs) have been considered as one of the most promising candidates for MOSFETs beyond 45 nm for future ultra-low power applications due to their better immunity to short channel effects, higher ION/IOFF ratio, and so on.[4–7] However, TFETs to date show a low drain current due to the low band-to-band tunneling (BTBT) efficiency.

To boost the tunneling currents, the biaxial strained silicon technology, which reduces the effective carrier transport mass (m*) by lowering and splitting the band gap resulting from the exerted strain in the silicon layer, seems to be an effective way to enhance the tunnel efficiency.[8–10] Gate all around TFETs (GAA TFETs) with strained silicon can provide enhanced electrostatic performance and optimum scaling capability to improve the current. The gate threshold voltage is a key electrical parameter for designing the TFET. Additionally, to estimate the device current we must know the threshold voltage.[11,12] Although plenty of efforts have been made for the extraction of TFET threshold voltages and some models have been developed, reports on the models for strained silicon TFETs with a GAA architecture have been rare.

In this paper, an analytical threshold voltage model for strained silicon GAA TFETs is developed. Moreover, the effect of the device parameters like the strain (Ge mole fraction x), gate oxide thickness, gate oxide permittivity, and channel length on the threshold voltage have been discussed, which can provide an effective reference for designing the GAA TFET. The model threshold voltage is extracted using peak transconductance method and is in excellent agreement with the TCAD simulation results, giving the evidence for its validity.

Figure

GAA TFET is basically a reverse biased PIN diode with the working principle of a quantum mechanical BTBT mechanism.[13] When a positive voltage is applied to the end of the gate and drain over the threshold voltage, the energy band at the source-channel junction is strongly bended, and valence and conduction band overlap occurs, as shown in Fig.

To predict the channel surface potential characteristic of the GAA TFET in the subthreshold region, we assume that the mobile charges in this region are negligible and that source-channel and drain-channel junctions are abrupt. Therefore, the 2D Poisson’s equation at the n-type strained silicon cylindrical channel can be written as

To obtain the solution of Eq. (

At the interface between the gate oxide and the strained silicon, we assume an electrostatic potential as a surface potential,

At the central axis of the cylinder channel, the electric field is zero,

At the interface between the gate oxide and the strained silicon, the electric field is continuous

Applying the boundary conditions from Eqs. (

The electric field distribution along the r radius direction can be written as

Substituting Eq. (

Equation (

The channel surface electric field along the z direction can be obtained as

To calculate the coefficients c1 and c2, we use the following boundary conditions:

By substituting Eqs. (

The threshold voltage is the gate voltage where the tunneling barrier width (tbw) from the valence band of the source region to the conduction band of the channel region starts to saturate with increasing applied gate bias. When tbw is around 5–6 nm, significant electron tunneling occurs.[15] Thus, the threshold voltage is the gate voltage when the gate voltage at z = tbw is equal to the surface potential Vds + ϕd, that is Vth = Vgs.

By substituting Eqs. (

The analytical model is verified by comparing the model results with Sentaurus TCAD simulation results. To obtain a more accurate simulation result, the nonlocal Kane’s BTBT model, band gap narrowing model, and SRH recombination model are used in the Sentaurus TCAD tools. The doping concentrations of Ns = 1020 cm−3 in the p-type source region, Nc = 1017 cm−3in the n-type channel, and Nd = 1019 cm−3 in the n-type drain region. The gate work function is Φ = 4.6 eV, and the gate leakage current is neglected in all the Sentaurus TCAD simulations.

The analytical results of the channel surface potential distribution as well as comparison to the TCAD simulations results for the different gate voltages applied and the different Ge mole fractions of x = 0.1, x = 0.2, and x = 0.3 are shown in Figs.

| Fig. 3. (a) Surface potential distribution along with the channel for different Ge mole fractions x. (b) Surface potential distribution along with the channel for the different gate voltage. |

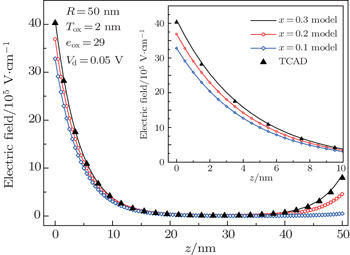

Figure

To verify the threshold voltage analytical model, a TCAD simulation was used. The model threshold voltage is extracted using the peak transconductance method. In Figs.

Figure

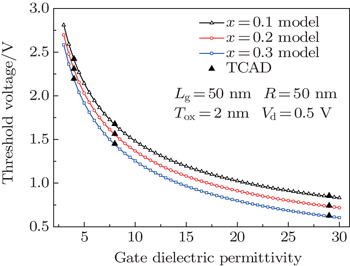

The variation of threshold voltage for different values of gate oxide permittivity and gate oxide thickness with the Ge mole fraction x = 0.1, x = 0.2, and x = 0.3 are shown in Figs.

In Fig.

Therefore, in order to obtain improved characteristics of the GAA TFET, a high k material and thinner oxide layer is chosen. The proposed model results coincide well to those of the TCAD simulation results.

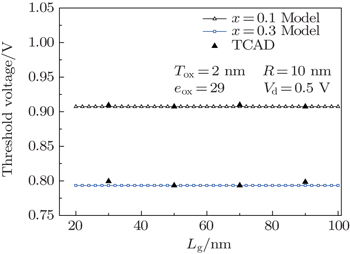

The variation of the threshold voltage with the length of the gate at constant drain and gate voltages is shown in Fig.

In summary, an analytical threshold voltage model that is based on the surface potential and electric field models obtained by solving the 2D polar coordinate Poisson’s equation in the channel for a strained silicon GAA TFET has been developed. Furthermore, it can be observed that the proposed model can predict the trend of the threshold voltage with the key TFET parameters. Our results show that the threshold voltage decreases with increasing Ge mole fraction x, and the gate dielectric permittivity increases with increasing gate oxide thickness. Superior to the MOSFET device, the threshold voltage of the TFET remains constant when the length of the gate increases. Therefore, to obtain improved characteristics of the GAA TFET, a high-k material, and thin oxide layer, and strain for x = 0.3 in Si1−xGex can be chosen. The proposed models provide an effective reference for the design and application of the GAA TFET.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 |