Improvement in the electrical performance and bias-stress stability of dual-active-layered silicon zinc oxide/zinc oxide thin-film transistor

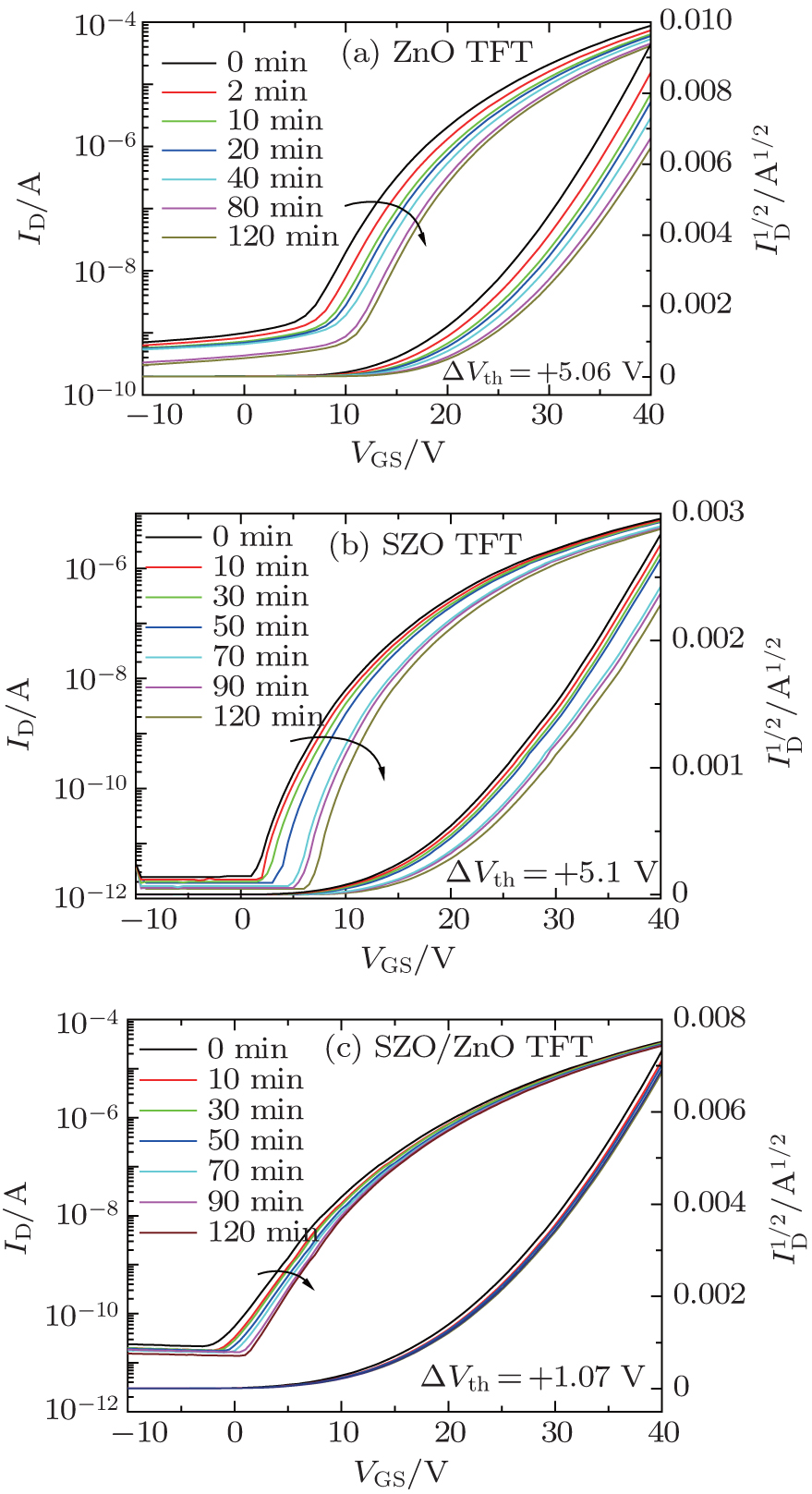

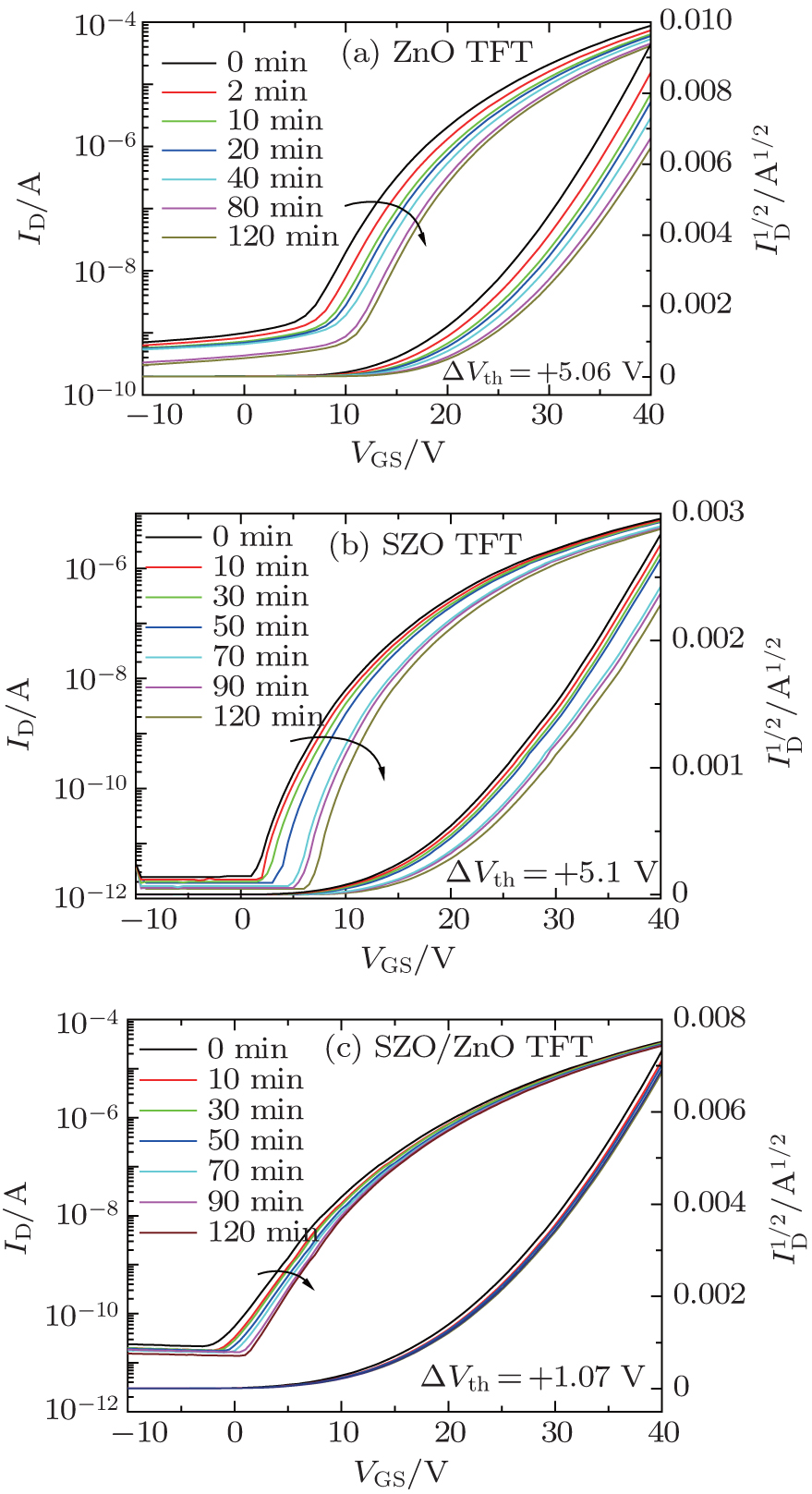

Transfer characteristics of the ZnO-based TFTs with single- and dual-active-layer structures at

Improvement in the electrical performance and bias-stress stability of dual-active-layered silicon zinc oxide/zinc oxide thin-film transistor |

Transfer characteristics of the ZnO-based TFTs with single- and dual-active-layer structures at |

|