An analytical model for nanowire junctionless SOI FinFETs with considering three-dimensional coupling effect

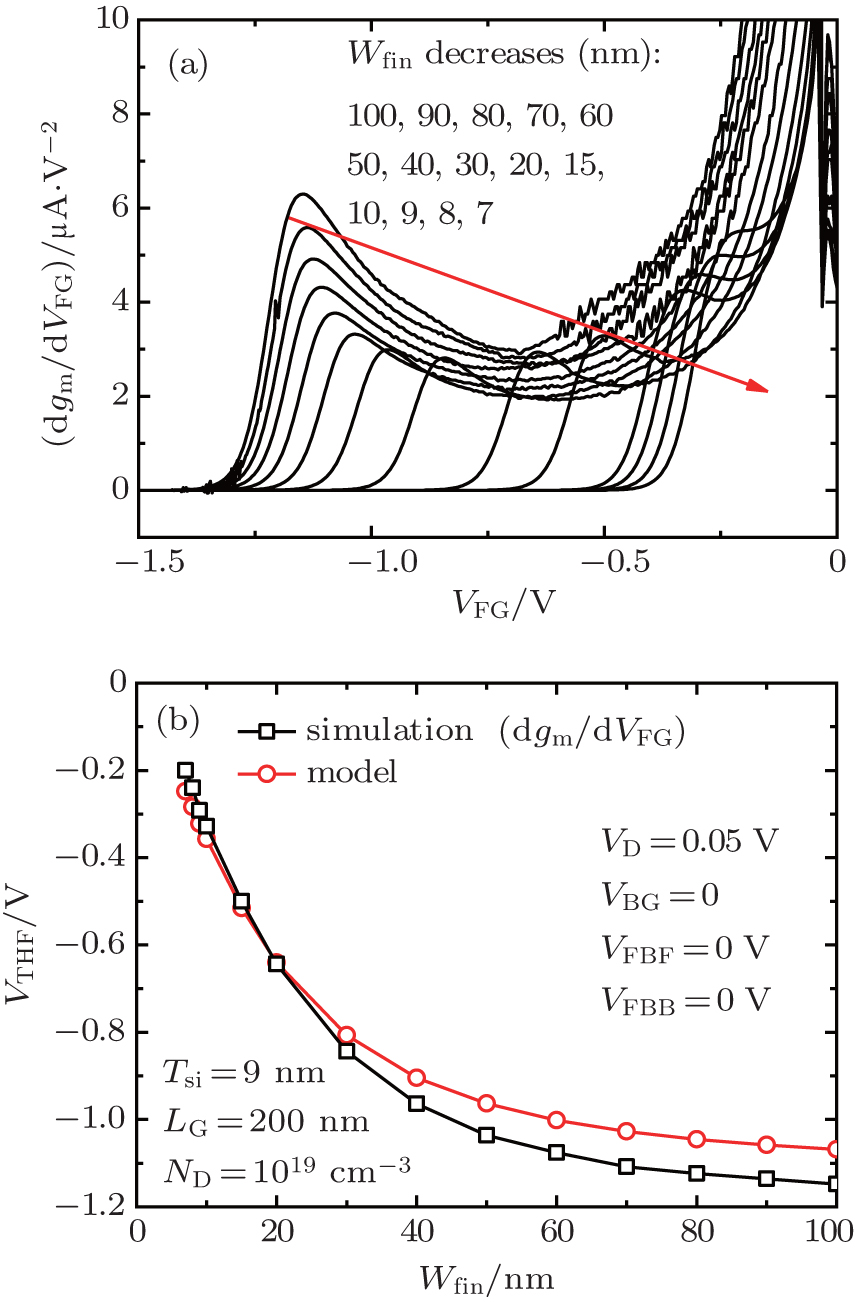

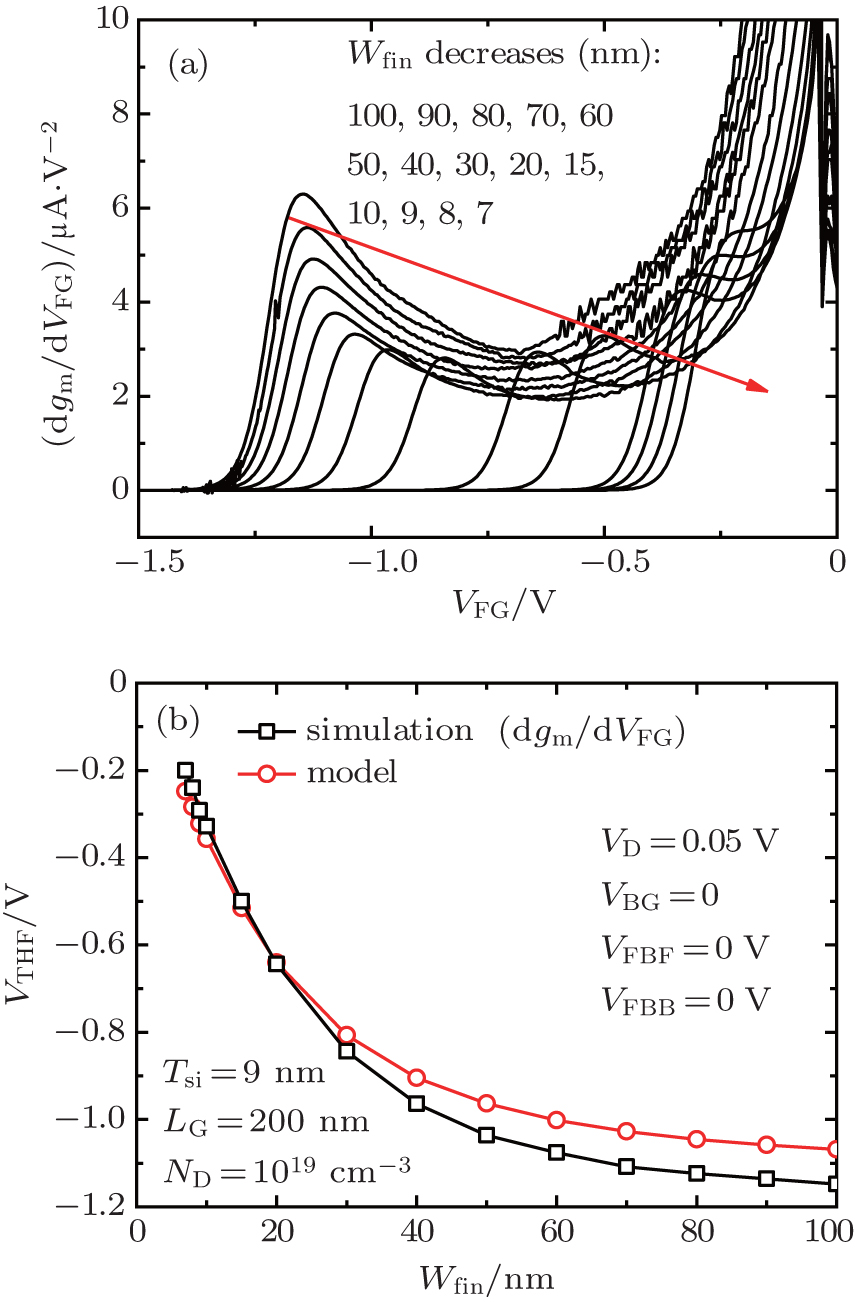

(a) Plots of simulated d

An analytical model for nanowire junctionless SOI FinFETs with considering three-dimensional coupling effect |

(a) Plots of simulated d |

|