An ultra-low specific on-resistance trench LDMOS with a U-shaped gate and accumulation layer

An ultra-low specific on-resistance trench LDMOS with a U-shaped gate and accumulation layer |

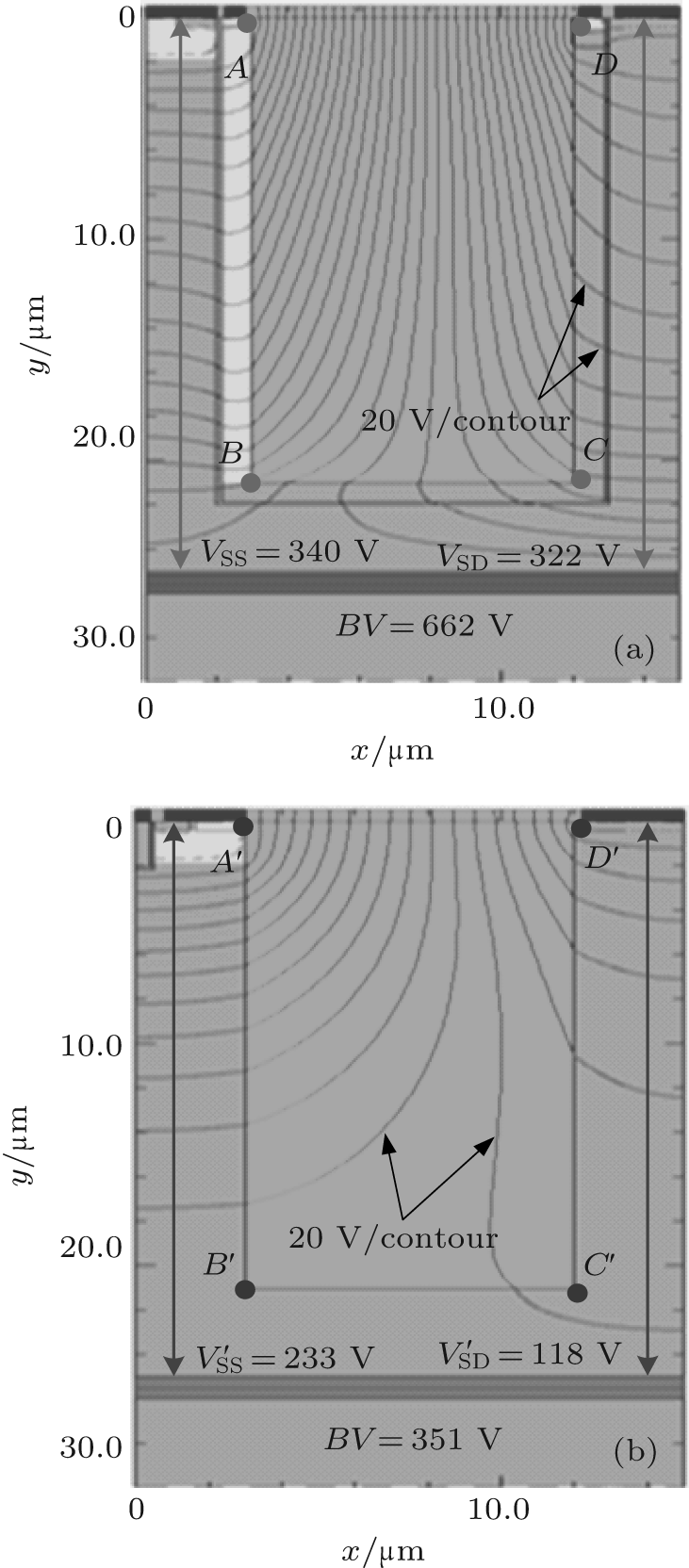

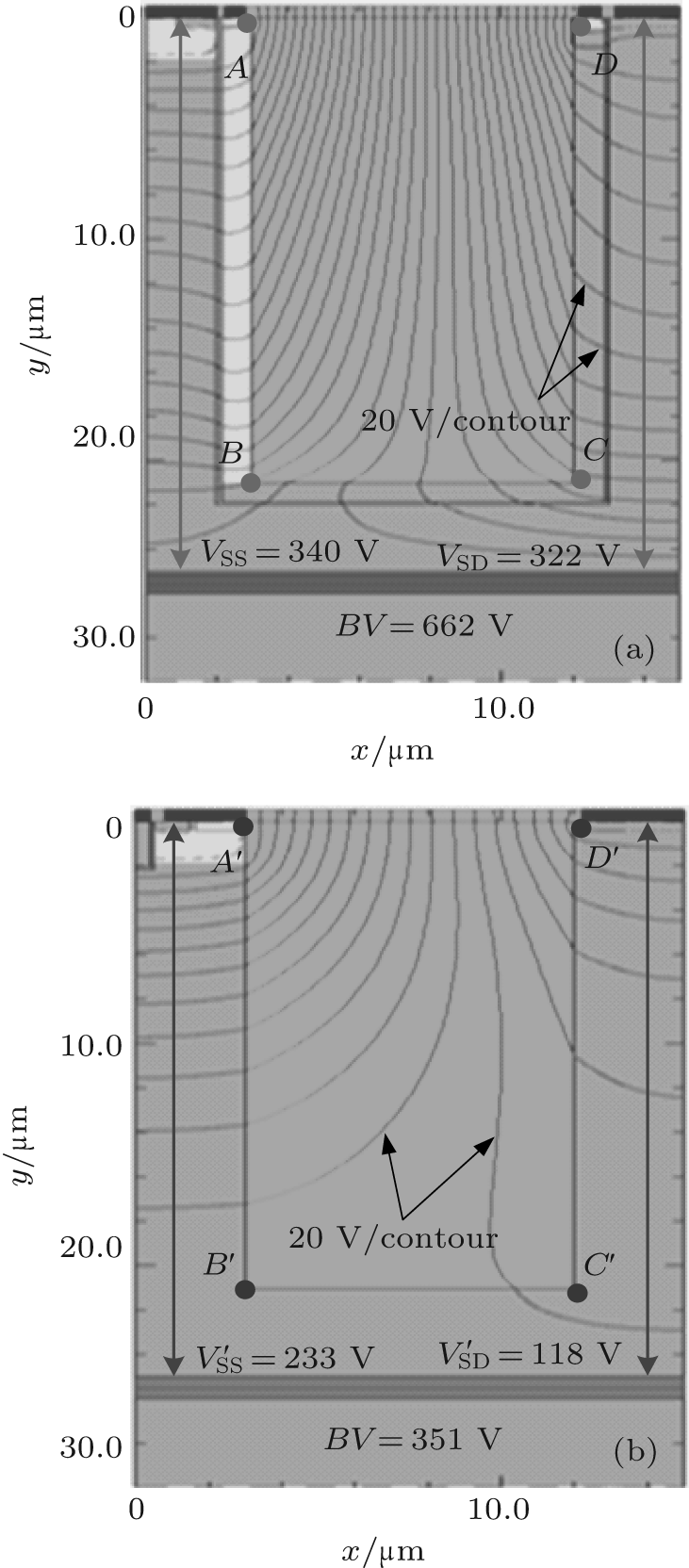

| Equi-potential contours at breakdown voltage for (a) UG LDMOS (662 V) and (b) CT LDMOS (351 V). |

|