† Corresponding author. E-mail:

A two-dimensional model of the silicon NPN monolithic composite transistor is established for the first time by utilizing the semiconductor device simulator, Sentaurus-TCAD. By analyzing the internal distributions of electric field, current density, and temperature of the device, a detailed investigation on the damage process and mechanism induced by high-power microwaves (HPM) is performed. The results indicate that the temperature elevation occurs in the negative half-period and the temperature drop process is in the positive half-period under the HPM injection from the output port. The damage point is located near the edge of the base–emitter junction of T2, while with the input injection it exists between the base and the emitter of T2. Comparing these two kinds of injection, the input injection is more likely to damage the device than the output injection. The dependences of the damage energy threshold and the damage power threshold causing the device failure on the pulse-width are obtained, and the formulas obtained have the same form as the experimental equations, which demonstrates that more power is required to destroy the device if the pulse-width is shorter. Furthermore, the simulation result in this paper has a good coincidence with the experimental result.

As a form of high electromagnetic wave, high-power microwave (HPM) will cause the semiconductor device to fail or burn out through the front door coupling and the back door coupling,[1] thereby affecting the normal operation of the whole circuit system. With electronic information technology development, the electromagnetic environment is becoming more and more complex. The influence of HPM on modern semiconductor devices and circuit systems has received increasing attention.[2–12]

A simulation of a bipolar junction transistor (BJT) with the high electromagnetic pulses injection from the collector was simulated by utilizing the finite difference time domain method in two dimensions, the results indicated that the damage spot lay between the emitter and the collector where the avalanche breakdown occurs.[13] The transient response characteristics were simulated using the improver two-dimensional semiconductor device simulation program in order to obtain the damage effect of the BJT under the injection of electromagnetic pulse, which showed that the peak temperature appears on the edge of the emitter.[14] In Ref. [15], a typical silicon-based n+–p–p–n+ structure of BJT caused by HPM is built, the simulation results revealed that the most vulnerable point of the device located at the cylinder of the base–emitter junction with the signals injected from the collector. Besides, the device is more easily destroyed with the signals injected from the base compared with the signals injected from the collector. In Ref. [16], the HPM pulse signal is injected into the base of a BJT, both the simulation results and the experimental results demonstrated that the induction voltage pulse generated by the HPM signal resulted in the destruction of the base area and a large amount of fuse and defects, which cause the device to fail. The effect of electromagnetic pulses (EMP) on a BJT with the base injection was investigated by numerical simulation and theoretical study, it was found that the hot spot is located at the edge of the base because the peak value of the electric field and the current density are at this point, where the heat generation is concentrated, and the energy needed for burnout is the smallest compared with two other forms of injection.[17] The amplitude of the injection pulse signal at the base is one of the influencing factors on the damage mechanism and damage points,[18] the simulation results showed that the transistor was destroyed by reverse avalanche breakdown of the base–emitter junction at low pulse amplitude, and the transistor was burned out due to secondary breakdown of the p–n–n+ diode consisting of the base region, epitaxial layer, and substrate at the high pulse amplitude. The damage effect experiment on a silicon low-noise amplifier (LNA) with base terminal injected microwave pulse signal was carried out, indicating that the local silicon material will be eroded and damaged at the base region as long as the microwave power is large enough, which leads to the short-circuit of the base–emitter and the base–collector junction, resulting in the failure of the transistor.[19] Using a combination of the simulation and the experimental results, the energy injected tests on an Si and GaAs bipolar LNA were performed, the results demonstrated that the damage point was between the base and emitter of T2. Meanwhile, the experiments on a silicon LNA showed that the passive resistance inside the LNA is also a vulnerable and weak link under the action of external energy.[20–22]

A composite transistor is widely used in large load driving circuits, power amplifier circuit, switch circuit, and automatic control circuit because of its advantages such as large current, high gain, small volume, fast switching speed, and easy integration. To improve the gain and the stability of the composite transistor, two kinds of structures are proposed, which are hybrid and monolithic composite transistor structures, recently.[23–25] However, researchers focused more on the gain and the stability of composite transistor than its damage effects caused by the harmful electromagnetic wave, so it is of great significance to study the influence of high-power microwave on this device. In this paper, a two-dimensional electro-thermal model of a silicon monolithic composite transistor is established for the first time by using the device simulator, Sentaurus-TCAD. The damage effect and mechanism is studied with the injection of HPM signal into the collector (output port) or base (input port) of the device, and the microwave pulse-width effects are given at the end of this paper. Moreover, we give a comparison of the simulation results and the experimental results, which verifies the correctness of the works.

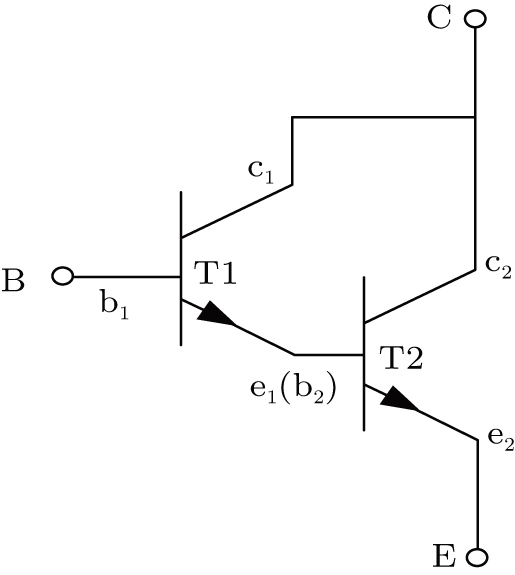

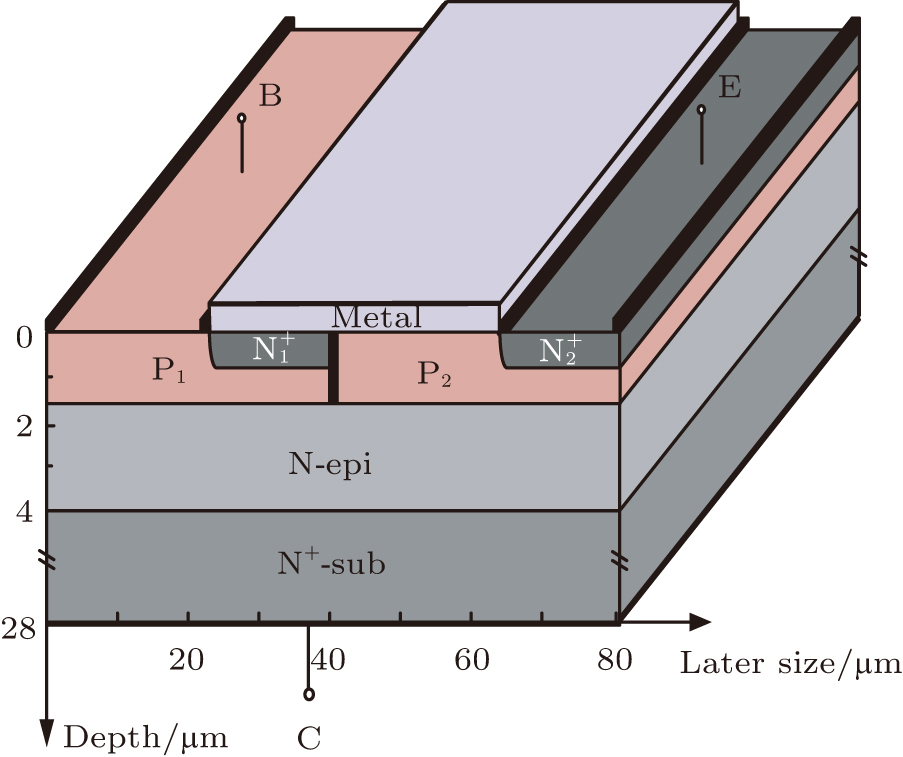

A circuit structure of the composite transistor used in our simulation is illustrated in Fig.

Figure

To investigate the damage effects and mechanism of the composite amplifier, it is necessary to compute the electrical behavior of the device by employing a device simulator to iteratively solve the Poisson equation and the current-continuity equations. Owing to the high bias voltage and current of the device during microwaves signal injecting, the contribution of the temperature gradient to the current density should be taken into consideration, the current density equation of electrons and holes is modified to

|

|

Besides, the effect of the internal temperature of the device on the carrier generation–recombination process needs to be taken into account. The carrier generation–recombination process considers carrier avalanche generation, SRH, and Auger recombination on which it takes the effect of doping concentration and temperature. An avalanche model named the van Overstraeten–de Man model[26] is used to describe the generation process of the electron–hole pair, and avalanche generation rate G is

|

|

|

In this paper, the HPM signal model is equivalent to a sinusoidal signal, the mathematical expression is as follows:

|

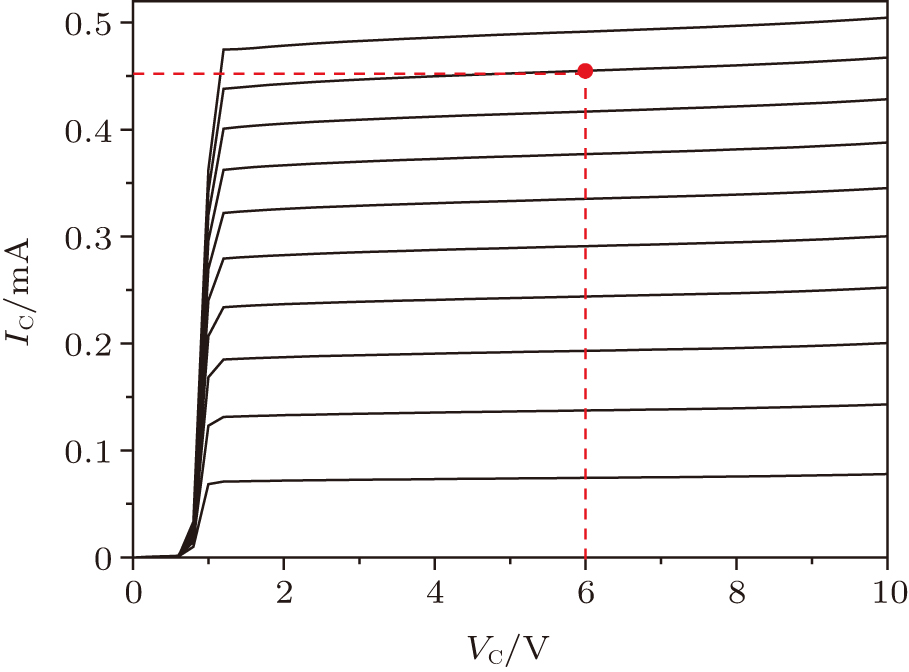

The input–output characteristic curve of the monolithic composite transistor is plotted in Fig.

| Fig. 3. (color online) The input–output characteristic curve of the monolithic composite transistor. |

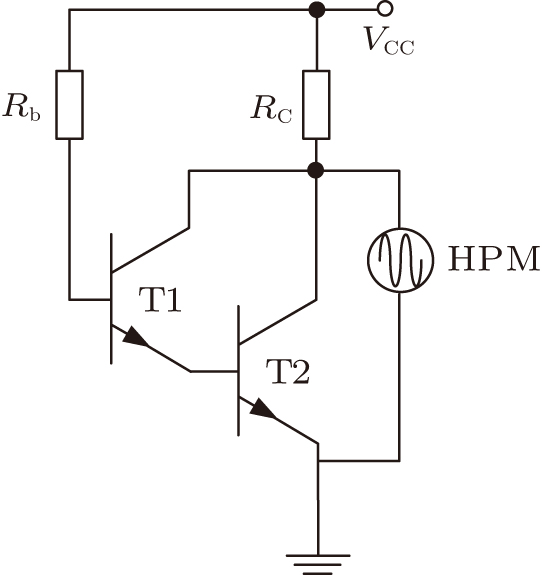

A schematic representation of the composite transistor operating in the state of amplification is shown in Fig.

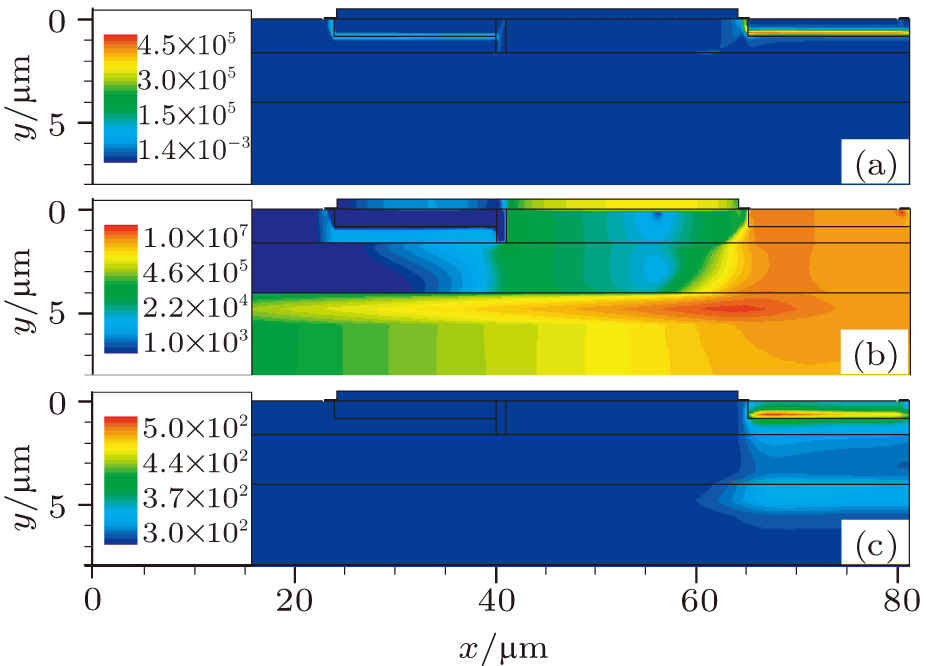

At the beginning of the negative half-period, the composite transistor is in the active mode of operation. When the absolute value of the signal voltage is increased to 1.25 V, the base–emitter junction of T1 and T2 s is reverse-biased while the base–collector junction is forward-biased. It should be noted that the electric field strength (

| Fig. 6. (color online) The distribution of (a) electric field, (b) current densities, and (c) lattice temperature at t = 3.75 ns. |

At the beginning of the positive half-period, the base–emitter junction of T1 and T2 is forward-biased, and the base–collector junction is reverse-biased, which means that the composite transistor is in the active mode of operation. The distribution of

| Fig. 7. (color online) The distribution of the electric field at (a) t = 3.05 ns, (b) t = 3.15 ns, and (c) t = 3.25 ns. |

The peak electric field lies in the n–n+ interface due to the effect of space charge modulation. The avalanche breakdown occurs when

| Fig. 8. (color online) The distribution of (a) current densities and (b) temperature at t = 3.25 ns. |

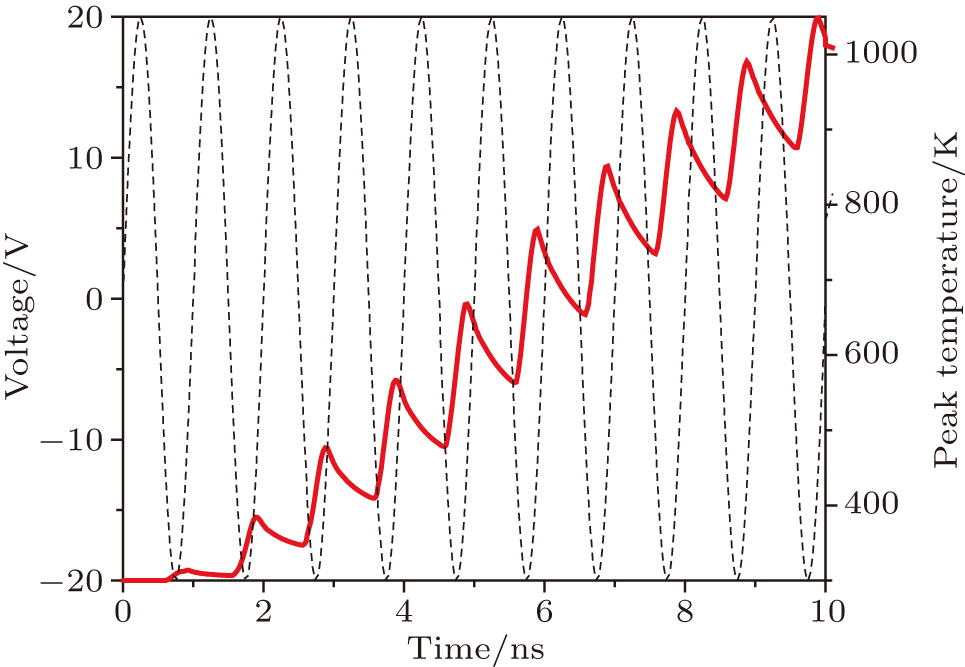

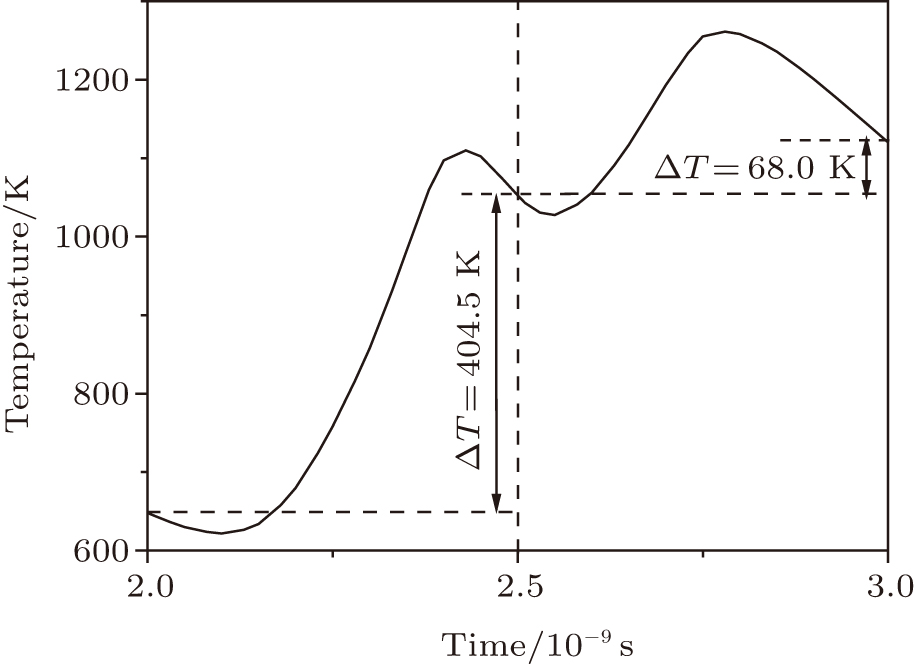

A conclusion can be made from the previous analysis that the peak temperature of the composite transistor decreases in the positive half-period, while the temperature elevation of the device occurs in the negative half-period. With the signal voltage continued, the maximum temperature variations have a periodic trend of “decrease–increase” until the temperature at the damage point reaches the melting point of silicon.

In this section, the damage process is explored when the sinusoidal voltage signal with an amplitude of 15 V is injected directly into the input port of the device. The simulation circuit is plotted in Fig.

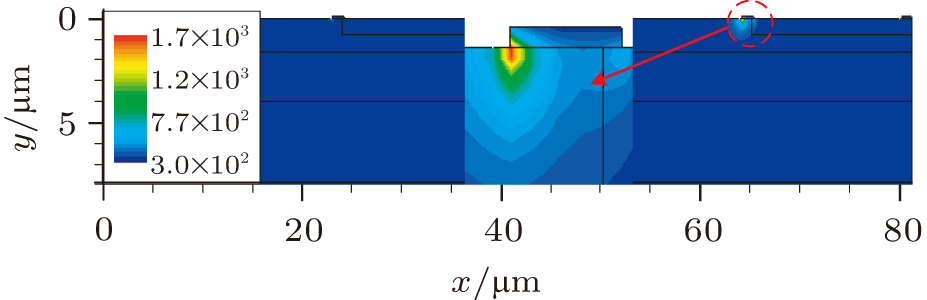

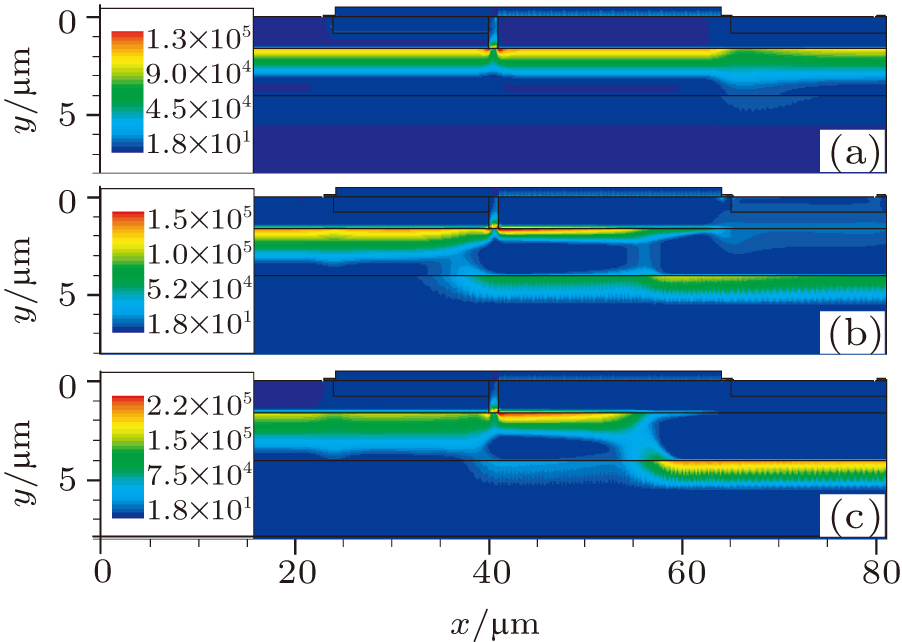

In the positive half-period, with the amplitude of the signal increasing, both the B–E junctions of T1 and T2 are forward-biased, which causes the forward current flowing through these two pn junctions, and the current grows exponentially. Particularly, the current concentrates upon the edge of the pn junction and the magnitude of the current is large (107 A/cm2). The temperature variation within the device is mainly affected by the current density with the input port injection, besides, considering the effect of protection resistances on T1, the current density of the B–E junction of T2 is larger than that of T1 (see Fig.

| Fig. 10. (color online) The distribution of the current densities at (a) t = 2.25 ns and (b) t = 2.75 ns. |

As shown in Fig.

Figure

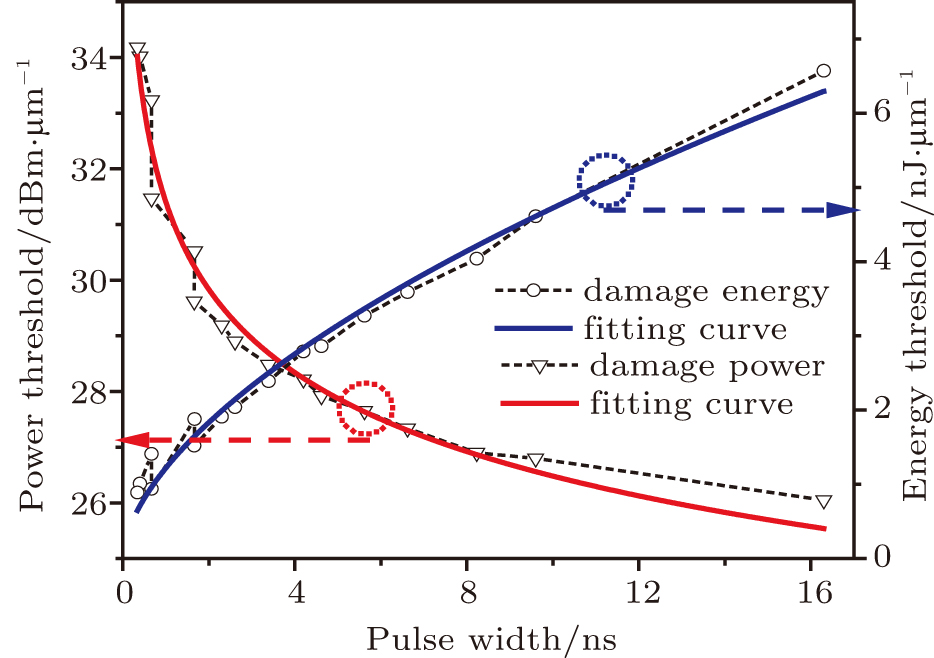

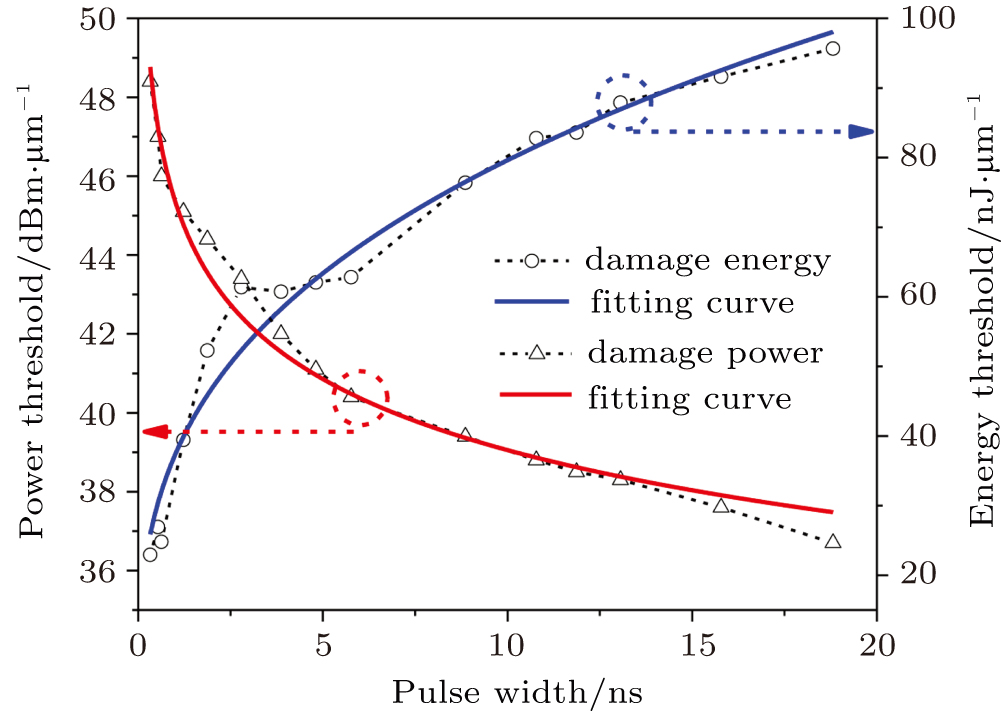

To provide a good prediction of semiconductor device damage and a guiding significance for HPM destruction, the dependence of the damage power threshold, P, and the damage energy threshold, E on the pulse-width under the output and input injection are obtained. In this paper, the pulse-width (τ) is defined as the time duration of the injected signal before the device is burned down, and the damage power threshold and the damage energy threshold as the average power and the total absorbed energy, respectively.

The variations of P and E with τ under the injection of output port are shown in Fig.

|

|

| Fig. 14. (color online) Damage power and damage energy versus pulse-width with the output injection. |

The dependence of the damage power and the damage energy on the pulse-width with the input injection are illustrated in Fig.

|

|

Comparing Fig.

In this paper, a two-dimensional model of a silicon NPN monolithic composite transistor structure is established firstly using the semiconductor device simulator. A detailed investigation on the damage process and mechanism caused by HPM is performed by analyzing the distribution of electric field, current density, and temperature of the device. The analysis reveals that temperature elevation processes appear in the negative half-period because both the peak electric field and the maximum current density lie in the edge of the B–E junction of T2 when HPM is injected from the output port, while the temperature decreases in the positive half-period. There is only one hot spot under the output injection, which locates near the edge of the B–E junction of T2, while for the injection from the input port, the damage point exists between the base and the emitter of T2. Compared with the output port injection, the input port injection is easier to destroy the device. By adopting the fitting software, the dependence of the damage energy, E, and the damage power, P, on pulse-width are obtained, respectively. The fitting formulas demonstrate that the damage energy threshold rises while the power threshold falls with the pulse-width increasing. Furthermore, the simulation results in this paper have a good coincidence with the experiment results. The findings of this paper are helpful to investigate the mechanism and protection of high-power microwave damage on semiconductor devices and circuits.

| [1] | |

| [2] | |

| [3] | |

| [4] | |

| [5] | |

| [6] | |

| [7] | |

| [8] | |

| [9] | |

| [10] | |

| [11] | |

| [12] | |

| [13] | |

| [14] | |

| [15] | |

| [16] | |

| [17] | |

| [18] | |

| [19] | |

| [20] | |

| [21] | |

| [22] | |

| [23] | |

| [24] | |

| [25] | |

| [26] | |

| [27] | |

| [28] |