† Corresponding author. E-mail:

Project supported by the National Natural Science Foundation of China (Grant Nos. 61376109, 61434007, and 61176030).

Charge sharing is becoming an important topic as the feature size scales down in fin field-effect-transistor (FinFET) technology. However, the studies of charge sharing induced single-event transient (SET) pulse quenching with bulk FinFET are reported seldomly. Using three-dimensional technology computer aided design (3DTCAD) mixed

With technology scaling beyond 22-nm node, traditional planar transistors are vulnerable to undesirable short channel effects (SCEs), which present the most important constraints to complementary metal–oxide–semiconductor (CMOS) scaling rules. Owing to the superior electrostatic scalability and better gate controllability over the channel (fin), Fin field-effect-transistors (finFETs) are widely recognized as a most promising candidate for traditional bulk CMOS transistors.[1,2] As a consequence, FinFET technologies are currently becoming the mainstream process in the leading semiconductor manufacturers.[3]

The pulse quenching has been reported in CMOS logical circuits and is widely identified as the result of multi-node charge collection between the electrically related transistors.[4–6] This would reduce the propagated single-event transient (SET) pulse width, which is beneficial to reducing the soft errors.[7,8] Much work has been done to investigate the pulse quenching in planar CMOS logic circuits.[9–12] As the feature size of transistor and space between devices scale down, the charge sharing effect (also called the multi-node charge collection) is becoming an important topic in FinFET technology.[13,14] However, to the best of our knowledge, little work has been done on the SET pulse quenching in those novel FinFET devices. Besides, with the reducing supply voltage as technology scales down, body-biasing has become an efficient control technique for optimizing the performance and power of devices.[15,16] The charge collection and well potential will also be affected by body-biasing when a single-event occurs in the circuit.[17] Thus, it is important to analyze the effects of body-biasing on charge collection and the resulting SET pulse quenching in the FinFET process.

In the present work, 3D TCAD mixed-mode simulations are performed to investigate the influences of supply voltage and body-biasing on the pulse quenching effect in a two-stage inverter chain in bulk FinFET process. Simulation results show that the SET pulse propagated to the passive p-FinFET decreases with supply voltage decreasing. Moreover, compared with the reverse body-biasing (RBB) circuit, the forward body-biasing (FBB) circuit is vulnerable to charge sharing and exhibits a mitigation of the propagating SET pulse about 53% at least. The rest of this paper is organized as follows. In Section 2 the TCAD simulation setup is presented. In Section 3 the simulation results are provided and the influences of supply voltage and body-biasing on SET pulse quenching are discussed. Finally, the conclusions are drawn from the present study in Section 4.

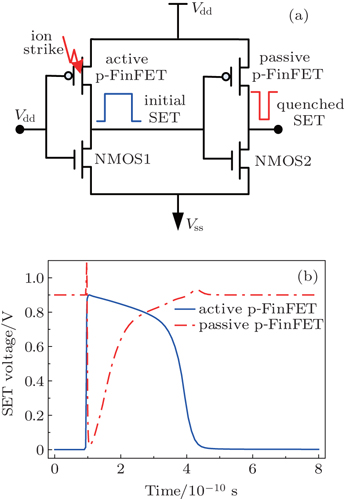

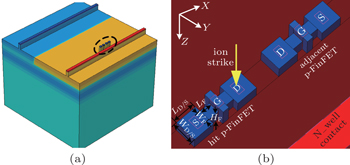

Synopsys Sentaurus TCAD H-2013.03-SP1 is employed to investigate the effects of supply voltage and body-biasing on the pulse quenching in a two-stage inverter chain under bulk FinFET process. Figure

| Fig. 1. (a) 3D TCAD model of the two bulk p-FinFETs in the dual-well process, (b) a zoomed view of the hit p-FinFET and the adjacent p-FinFET. |

| Table 1. Geometrical structure parameters of the p-FinFET. . |

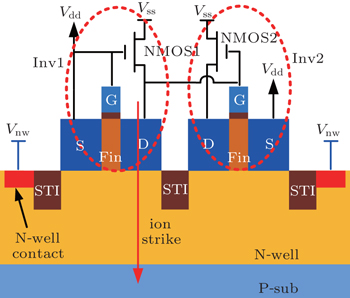

| Fig. 2. Schematic configuration of the mixed-mode simulation setup for a two-stage inverter chain. The TCAD p-FinFETs are cut in the middle of the gate along the source/drain direction (X–Z plane). |

As illustrated in Fig.

In the following sections, the p-FinFET struck by heavy-ion is defined as the active device, while the adjacent p-FinFET is termed the passive device. The space between the active and passive FinFETs is 120 nm, and simulations are conducted for normal strike on the drain center of the active device with an ion linear energy transfer (LET) value of 20 MeV·cm2/mg. The following physical models are used in the simulations: 1) Fermi–Dirac carrier statistics; 2) band-gap narrowing effect; 3) doping-dependent Shockley–Read–Hall (SRH) and Auger recombination; 4) effects of temperature, doping, electric field, and carrier–carrier scattering on mobility; 5) a hydrodynamic model is used for the carrier transportation equations; and 6) incident heavy ions are modeled by using a Gaussian radial profile with a characteristic 1/e radius of 50 nm and a Gaussian temporal profile with a characteristic decay time of 0.25 ps.

In this simulation, the N-well contact is connected to the supply voltage Vdd (also called zero body-biasing (ZBB)), and the circuit with different supply voltages varying from 0.7 V to 1.1 V is simulated to investigate the voltage dependence of SET pulse width.

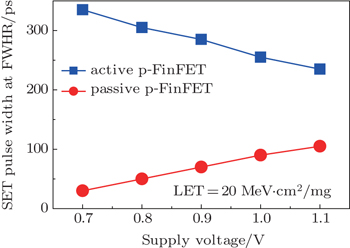

Figure

As shown in Fig.

| Fig. 3. The SET pulse width at FWHR captured in active and passive p-FinFETs with different supply voltages. The ion LET is 20 MeV·cm2/mg. |

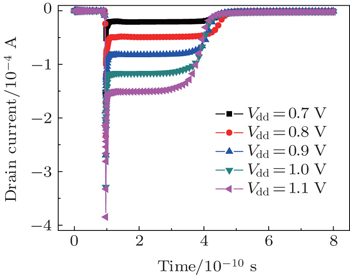

| Fig. 4. Current transients captured in the drain of hit p-FinFET at different supply voltages for normal mode. The ion LET is 20 MeV·cm2/mg. |

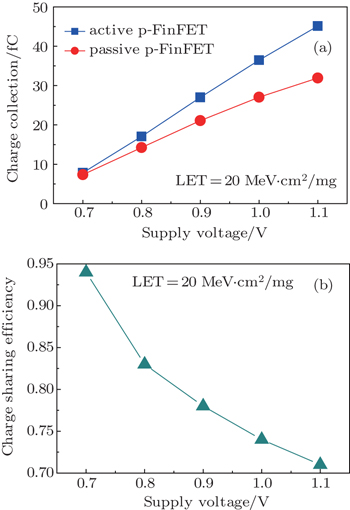

However, the SET pulse propagating to the passive p-FinFET increases with supply voltage increasing from 0.7 V to 1.1 V, which exhibits an opposite voltage dependence trend compared with the case in an active device. This can be explained by the single event charge sharing and the resulting pulse quenching effects between the proximal nodes which are electrically related to each other. As described in Ref. [4], the pulse quenching is determined by the competing mechanism between propagating SET electrical signal and the charge sharing induced SET pulse of the passive device. Owing to the reduced nodal spacing and high packing density in FinFET technology, a charge sharing effect occurs easily between the FinFET transistors. Figure

A great deal of work has highlighted the relationship between the SET pulse and the amount of charge collection in an inverter chain, which shows that when the voltage applied to the complementary transistor is fixed, the SET pulse width is proportional to the charge collection. To ensure that the charge collected in a passive device is caused by the charge sharing effect, the same circuit configuration and hit location as shown in Fig.

Figures

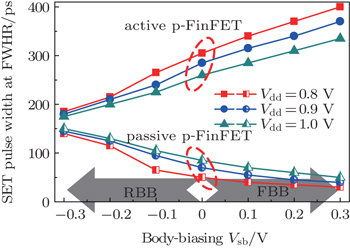

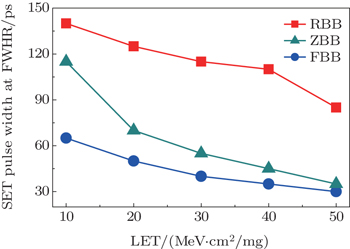

In this simulation, the N-well contact is biased at a voltage separated from Vdd. The circuits with different body-biasing modes (FBB, RBB, and ZBB) are simulated to investigate the effect of body-biasing on the SET pulse quenching in the bulk FinFET process. The bias voltage varies from −0.3 V to 0.3 V. That is, the negative value refers to RBB, while the positive value corresponds to FBB.

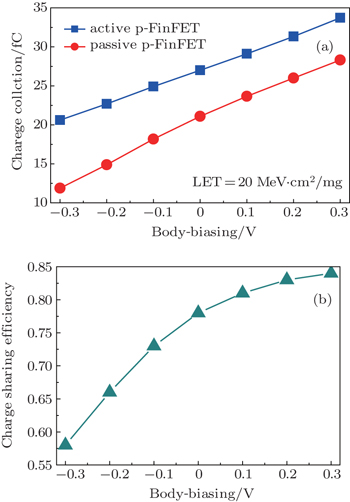

The simulated results are shown in Fig.

In our previous work, we illustrated that the bipolar amplification induced by the N-well can exert important effects on the charge collection and SET pulse width in bulk p-FinFETs.[20,21] The body-biasing can affect the potential barrier between the source and N-well, which is a key factor for the parasitic bipolar junction transistor (BJT_Well) to be turned on. The injection hole current from source to the N-well is calculated as[22]

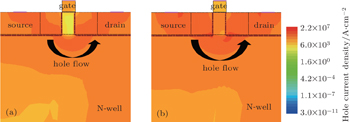

| Fig. 8. Hole current flowing in the passive p-FinFET for different body-biasing voltages at 20 ps after ion strike: (a) RBB; (b) FBB. |

| Fig. 9. Hole currents of drain and source terminating in the passive p-FinFET for different body-biasing voltages at 0.2 V (FBB = 0.2 V, RBB = −0.2 V). The ion LET is 20 MeV·cm2/mg. |

Figures

| Fig. 10. (a) Charge quantities collected in active and passive devices and (b) the corresponding charge sharing efficiency versus body-biasing, with the ion LET being 20 MeV·cm2/mg. |

As shown in Fig.

According to the 3D TCAD mixed-mode simulation, we investigate the effects of supply voltage and body-biasing on the SET pulse quenching in bulk FinFET process. The proposed CSE factor is used to determine the characteristics of SET pulse width between the active and passive p-FinFETs. According to the simulation results, the SET pulse propagating to the passive device decreases when reducing the supply voltage. The results also indicate that owing to an enhanced bipolar amplification effect, the circuit with FBB is more vulnerable to charge sharing than that with RBB. The propagating pulse in FBB mode is truncated up to 53% compared with that in RBB mode. This is very important in the advanced nano-scale FinFET circuit for the single-event effect, and can provide guidance for radiation-hardened bulk FinFET technology, especially in low power and high performance applications.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 | |

| 16 | |

| 17 | |

| 18 | |

| 19 | |

| 20 | |

| 21 | |

| 22 |