† Corresponding author. E-mail:

‡ Corresponding author. E-mail:

Projcet supported by the National Natural Science Foundation of China (Grant Nos. 61404098, 61176070, and 61274079), the Doctoral Fund of Ministry of Education of China (Grant Nos. 20110203110010 and 20130203120017), the National Key Basic Research Program of China (Grant No. 2015CB759600), and the Key Specific Projects of Ministry of Education of China (Grant No. 625010101).

In this paper, the normally-off N-channel lateral 4H–SiC metal–oxide–semiconductor field-effect transistors (MOSFFETs) have been fabricated and characterized. A sandwich- (nitridation–oxidation–nitridation) type process was used to grow the gate dielectric film to obtain high channel mobility. The interface properties of 4H–SiC/SiO2 were examined by the measurement of HF I–V, G–V, and C–V over a range of frequencies. The ideal C–V curve with little hysteresis and the frequency dispersion were observed. As a result, the interface state density near the conduction band edge of 4H–SiC was reduced to 2 × 1011 eV−1·cm−2, the breakdown field of the grown oxides was about 9.8 MV/cm, the median peak field-effect mobility is about 32.5 cm2·V−1·s−1, and the maximum peak field-effect mobility of 38 cm2·V−1·s−1 was achieved in fabricated lateral 4H–SiC MOSFFETs.

Due to excellent physical and electrical properties, such as high breakdown electric field, wide bandgap, high thermal conductivity, and high electron saturation velocity, silicon carbide (SiC) has attracted increasing attention in high-temperature, high-power, and high-voltage devices.[1–4] Metal–oxide–semiconductor field-effect transistors (MOSFETs) based on SiC have been regarded as a promising candidate for low-loss and fast power devices in advanced electronic systems.[5] Significant progress in 4H–SiC MOSFETs has been demonstrated recently, with the fabrication of accumulation-mode MOSFETs (ACCUFETs),[1] UMOSFET,[2,6] DMOSFET,[7–10] and RESURF MOSFET.[11] SiC lateral MOSFETs are also very attractive as high-frequency power transistors, which can favorably compete with Si lateral MOSFET.[11,12] SiC lateral devices have a distinctive advantage of being able to be integrated with other devices, reducing cost, and enhancing overall circuit performance.[11,13]

The growth of high-quality gate oxides (SiO2) with abrupt SiC/SiO2 interfaces, containing a low density of interface traps Dit, is crucial for the fabrication of reliable MOSFETs with high channel mobility on 4H–SiC.[14] The main source of the high Dit values has been attributed to residual carbon in the gate oxide layer,[15] which was observed in the form of clusters[16,17] distributed along the SiO2/SiC interface. Although the chemical nature of these clusters is still not completely understood, it has been related to carbon complexes and silicon oxycarbides (SiCxOy)[18] formed during the oxidation process. To form high-quality gate oxides with abrupt SiC/SiO2 interfaces, here a sandwich gate oxidation method[14] was used in our work. In this paper, our recent experimental work on N-channel enhancement lateral 4H–SiC MOSFFETs is reported. The lateral 4H–SiC MOSFFETs were successfully fabricated using ion implantation and sandwich (nitridation–oxidation–nitridation) type gate oxidation process. N-type MOS capacitors were also fabricated simultaneously with the lateral devices to investigate the interface properties of 4H–SiC/SiO2. The properties of 4H–SiC/SiO2 interfaces on N-type MOS capacitors were examined by the measurement of HF C–V, I–V, and G–V over a range of frequencies. High mobility of 38 cm2·V−1·s−1 was achieved for the fabricated lateral 4H–SiC MOSFFETs.

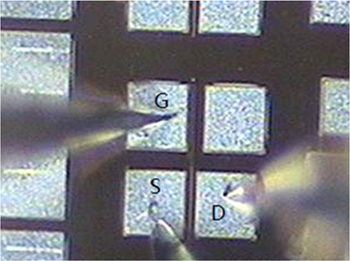

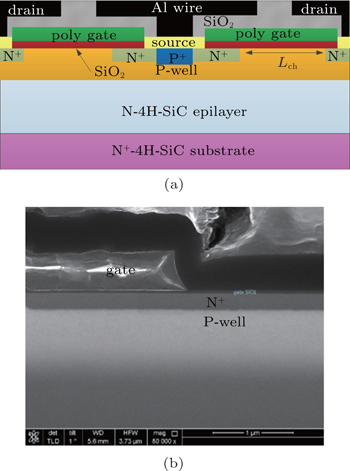

N-type 4°-off 4H–SiC (0001) Si-face epilayer with a net donor concentration of 6 × 1015 cm−3 was used to fabricate N-type MOS capacitors and lateral N-channel 4H–SiC MOSFFETs. A schematic cross section of the lateral N-channel 4H–SiC MOSFFETs and scanning electron microscopy (SEM) image of the fabricated device cross section are shown in Fig.

| Fig. 1. (a) Schematic cross section of the fabricated lateral N-channel 4H–SiC MOSFFETs and (b) scanning electron microscopy (SEM) image (cross section) of fabricated device. |

Prior to gate oxidation, the samples were prepared using RCA cleaning. The gate oxides were formed by the an NO/O2/NO sandwich-type process, which consists of a 2% NO pre-anneal for 1 hour, followed by the bulk oxide growth in 5% dry O2, finalized with a post oxidation anneal in 2% NO for an hour.[2] Next, a polysilicon film was deposited and patterned to form the gate contact. Finally, source and drain Ohmic contacts were formed by evaporating Ti/Ni/Al (50 nm/100 nm/200 nm) and annealing with rapid thermal processing (RTP).

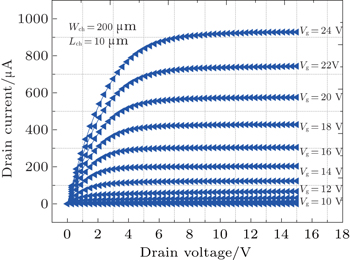

Thicknesses of the gate dielectric films were determined by both scanning electron microscopy (SEM), and capacitance–voltage (C–V) measurements. The channel length (Lch) and width (Wch) of the fabricated lateral MOSFETs were 10 μm and 200 μm, respectively. The MOS capacitors and MOSFET electrical properties (transfer and output characteristics) were measured with the Agilent B1505A semiconductor characterization system. All measurements presented in this paper were performed at room temperature.

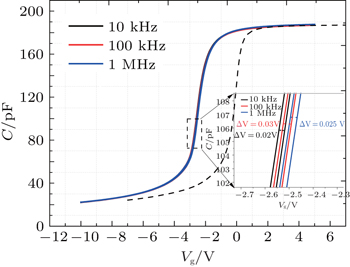

Figure

| Fig. 3. Bidirectional capacitance–voltage (C–V) characteristics measured with various frequencies from 10 kHz to 1 MHz for the MOS capacitor fabricated with NO/O2/NO sandwich oxidation. |

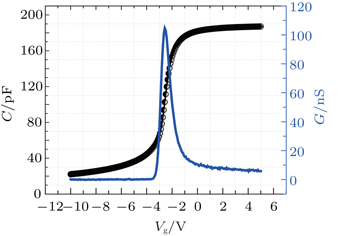

| Fig. 4. Conductance–voltage (G–V) and capacitance–voltage (C–V) curves at 10 kHz for the MOS capacitor fabricated with NO/O2/NO sandwich oxidation. |

| Table 1. Parameters of the MOS capacitor extracted from the C–V curve measured at 10 kHz. . |

Table

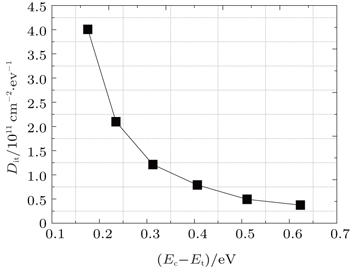

| Fig. 5. Distribution of interface state density (Dit) near the conduction band edge (Ec) of 4H–SiC estimated using the hi-lo C–V method. |

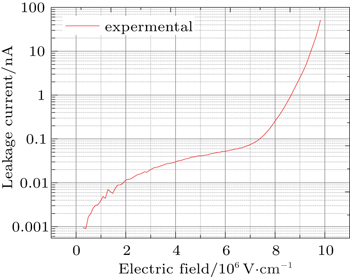

To evaluate the dielectric film breakdown characteristics, the typical current–electric field curves (I–E) of fabricated N-type 4H–SiC MOS structures is shown in Fig.

Figure

| Fig. 7. Typical output characteristics of the lateral enhancement mode N-channel MOSFET with gate voltage (Vg) from 0 V to 24 V and the drain–source voltage (VDS) from 0 V to 15 V. |

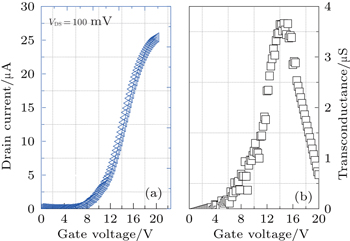

| Fig. 8. (a) Transfer characteristics of the fabricated devices measured at a drain voltage of 100 mV and (b) the corresponding transconductance characteristics. |

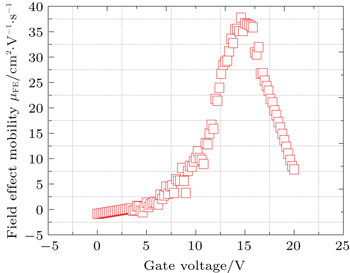

To examine the validity of the NO/O2/NO sandwich-type gate oxidation method, gate voltage dependence of the field-effect mobility μFE was measured, and the Vg for the measurement ranges from 0 to 20 V. The μFE can be calculated from the following formula using transconductance characteristic at the drain voltage of 100 mV:

The normally-off N-channel lateral 4H–SiC metal–oxide–semiconductor field-effect transistors (MOSFFETs) have been fabricated using sandwich (nitridation–oxidation–nitridation) type process in this paper. The interface state density near the conduction band edge of 4H–SiC was reduced to 2 × 1011 eV−1·cm−2, breakdown field of the grown oxides was about 9.8 MV/cm, and peak field-effect mobility of 38 cm2·V−1·s−1 was achieved. It is found that the NO/O2/NO sandwich-type oxidation process has a great potential as an alternative gate oxidation method in SiC MOS-based transistors.

| 1 | |

| 2 | |

| 3 | |

| 4 | |

| 5 | |

| 6 | |

| 7 | |

| 8 | |

| 9 | |

| 10 | |

| 11 | |

| 12 | |

| 13 | |

| 14 | |

| 15 | |

| 16 | |

| 17 | |

| 18 |