## Chemical Vapor Deposition Growth of Large-Area Monolayer MoS<sub>2</sub> and Fabrication of Relevant Back-Gated Transistor \*

Jian-Ying Chen(陈建颖)<sup>1</sup>, Lu Liu(刘璐)<sup>1</sup>, Chun-Xia Li(李春霞)<sup>2\*\*</sup>, Jing-Ping Xu(徐静平)<sup>1\*\*</sup>

<sup>1</sup>School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074

<sup>2</sup>Shenzhen Institution of Information Technology, Shenzhen 518172

## (Received 4 December 2018)

A closed two-temperature-zone chemical vapor deposition (CVD) furnace was used to grow monolayer molybdenum disulfide (MoS<sub>2</sub>) by optimizing the temperature and thus the evaporation volume of the Mo precursor. The experimental results show that the Mo precursor temperature has a large effect on the size and shape transformation of the monolayer MoS<sub>2</sub>, and at a lower temperature of  $<760^{\circ}$ C, the size of the triangular MoS<sub>2</sub> increases with the elevating temperature, while at a higher temperature of  $>760^{\circ}$ C, the shape starts to change from a triangle to a truncated triangle. A large-area triangular monolayer MoS<sub>2</sub> with a side length of 145  $\mu$ m is achieved at 760°C. Further, the as-grown monolayer MoS<sub>2</sub> is used to fabricate back-gated transistors by means of electron beam lithography to evaluate the electrical properties of MoS<sub>2</sub> thin films. The MoS<sub>2</sub> transistors with monolayer MoS<sub>2</sub> grown at 760°C exhibit a high on/off current ratio of 10<sup>6</sup>, a mobility of 1.92 cm<sup>2</sup>/Vs and a subthreshold swing of 194.6 mV/dec, demonstrating the feasible approach of CVD deposition of monolayer MoS<sub>2</sub> and the fabrication of transistors on it.

PACS: 73.63.Bd, 72.80.Vp, 74.25.nd DOI: 10.1088/0256-307X/36/3/037301

Two-dimensional materials such as graphene and transition metal dichalcogenides (TMDs)<sup>[1,2]</sup> have attracted great attention because of their unique features compared with conventional bulk materials. Molybdenum disulfide (MoS<sub>2</sub>), as a TMD, has an adjustable band gap and high on/off ratio compared with graphene, which means that photoelectric devices based on a back-gated MoS<sub>2</sub> transistor have broadband spectrum detection, lower dark current and high photoresponsivity.<sup>[2]</sup> There have been many reports on the fabrication of MoS<sub>2</sub> thin film, with micro-exfoliation being one of the earliest ways to prepare it. [3-5] However, exfoliation is not a reliable fabrication method as the size and thickness of the produced  $MoS_2$  flakes are uncontrollable. As an alternative, the chemical vapor deposition (CVD) method was employed and has been demonstrated to produce large-area and high-quality  $MoS_2$  films. [6-11] The sulfurization of solid molybdenum trioxide (MoO<sub>3</sub>) is the most common mechanism of CVD synthesizing  $MoS_2$ . Yet, the CVD growth of  $MoS_2$  is influenced by many factors. Yang et al. reported a systematical study of low-pressure CVD growth of high-quality crystals of monolayer  ${\rm MoS}_2.^{\hbox{\scriptsize [12]}}$  Cao et~al. investigated the influence of Ar flow rate on the morphology evolution. [13] Wang et al. used the shape transformation model to explain the shape change during the growth of  ${\rm MoS_2}$  thin films by CVD. [14] Xie et al. used  ${\rm MoO_2}$  as a precursor to grow large-area and high-quality mono-layer MoS<sub>2</sub>. [15] All of the above works were performed by placing S and Mo sources in a single temperaturezone furnace tube without considering the effects of their respective temperature. In a closed environment, the amount of reactants is mainly determined by the evaporation temperature, and changing the precursor temperature can affect the area of CVD-deposited thin

films.<sup>[16]</sup> By heating S and Mo sources separately in the tube, the reaction between S and Mo sources can be accurately controlled. Usually, the observed edge structures for the MoS<sub>2</sub> flakes are Mo zigzag (Mo-zz) and S zigzag (S-zz) terminations, which are supposed to be the most energetically stable structures. As reported, the shape of the monolayer MoS<sub>2</sub> results from the two types of zigzag edge terminations and can be changed by varying the amount of S and Mo sources.<sup>[17]</sup> Therefore, in this work, the effects of temperature on the growth of monolayer MoS<sub>2</sub> are investigated using a two-temperature-zone furnace tube and keeping the S source temperature unchanged and changing the Mo source temperature, so as to control the amount of supplied Mo precursor. The shape of the MoS<sub>2</sub> film is changed from a triangle to a truncated triangle when a large quantity of Mo precursor is provided. By optimizing the temperature, a large scale of over 120 µm or even 145 µm MoS<sub>2</sub> triangular islands are formed at a Mo source temperature of 760°C and an S source temperature of 220°C. Various microanalysis techniques are employed to characterize the structure, thickness and morphologies of the as-grown MoS<sub>2</sub> thin films, including Raman and photoluminescence (PL) spectra, atomic force microscopy (AFM) and scanning electron microscopy (SEM). The shape transformation is explained using the dependence on the atom ratio of Mo to S, which can provide a practical guide for growing large-area MoS<sub>2</sub> thin films. Finally, back-gated transistors based on the asgrown monolayer MoS<sub>2</sub> are fabricated to evaluate the electrical properties of the devices.

Heavily doped p<sup>+</sup> silicon with a resistivity of  $\sim 0.01 \Omega \cdot \text{cm}$  was used as the starting substrate. 30 nm SiO<sub>2</sub> was thermally grown on the Si substrate by dry oxidation. Prior to the MoS<sub>2</sub> growth, the SiO<sub>2</sub>/Si

<sup>\*</sup>Supported by the National Natural Science Foundation of China under Grant No 61774064.

<sup>\*\*</sup>Corresponding author. Email: jpxu@hust.edu.cn; licx@sziit.edu.cn

<sup>© 2019</sup> Chinese Physical Society and IOP Publishing Ltd

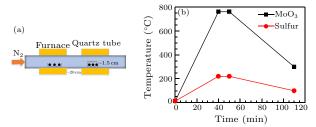

substrate was treated by oxygen plasma with a power of 60 W for 5 min, followed by CVD MoS<sub>2</sub> growth in a two-zone furnace system as shown in Fig. 1(a). An alumina boat with 500 mg S powders (99.99% Aladdin) was placed upstream in the low-temperature zone. Another alumina boat containing 5 mg MoO<sub>3</sub> powders (Ourchem) was placed downstream in the high-temperature zone. The SiO<sub>2</sub>/Si target substrate of  $12 \,\mathrm{mm} \times 12 \,\mathrm{mm}$  was face down placed on the top of the MoO<sub>3</sub> boat. The distance between the two alumina boats was 20 cm. This long distance was to ensure that the S vapor concentration gradient on the SiO<sub>2</sub>/Si substrate could be ignored, as compared with the MoO<sub>3</sub> concentration gradient. The S and MoO<sub>3</sub> sources were heated to 220°C and 720°C-780°C, respectively, under 100 sccm  $N_2$  carrier gas. Figure 1(b) shows the temperature programming process of the MoO<sub>3</sub> and S precursors. After keeping the temperature for 1 min, the furnace was naturally cooled down to room temperature. Raman and PL spectra were collected by a Horiba LabRAM HR 800 Raman microscopic system, where the power of the solidstate excitation laser was 0.5 mW with a wavelength of  $532 \,\mathrm{nm}$  and a  $100 \times$  objective was used to focus the laser beam. The SEM images were taken by a Gemini SEM 300-71-12 with an accelerating voltage of 10 kV. The shape and thicknesses of the MoS<sub>2</sub> thin film were characterized by an AFM (Bruker Dimension Edge SPM System). The as-grown MoS<sub>2</sub> triangular islands were used to fabricate the back-gated transistors using electron beam lithography. Poly(methyl methacrylate) and methyl methacrylate were spin-coated on the MoS₂ thin film successively, followed by 150°C baking. After pattern writing and development, Cr/Au (10/50 nm) were deposited by electron beam evaporation, and then an anneal was performed at 300°C for  $10 \,\mathrm{min}$  in  $95\%\mathrm{N}_2 + 5\%\mathrm{H}_2$  atmosphere to reduce the contact resistance between the Cr/Au and MoS<sub>2</sub>. The current-voltage (I-V) curve of the devices was measured using a Keithley4200-SCS parameter analyzer at room temperature in a dark ambient circumvent.

**Fig. 1.** (a) CVD furnace setup for the  $MoS_2$  growth, and (b) the temperature programming process of  $MoO_3$  and S precursors.

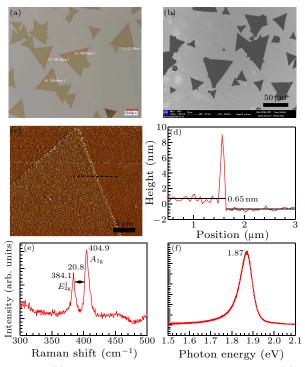

Figures 2(a) and 2(b) show the optical and SEM images of those  $MoS_2$  triangular islands synthesized at a Mo source temperature of 760°C, where the largest side length is 146  $\mu$ m. Figure 2(c) shows the AFM image of the  $MoS_2$  triangular islands. Its step height is  $\sim 0.65$  nm (Fig. 2(d)) along the black line in Fig. 2(c), which is consistent with the thickness of the monolayer  $MoS_2$  grown on a  $SiO_2/Si$  substrate.<sup>[18]</sup> Further,

the Raman spectrum is analyzed to confirm the MoS<sub>2</sub> structure. As shown in Fig. 2(e), two characteristic Raman vibration modes can be observed, where the  $E_{2g}^1$  mode represents the in-plane vibration molybdenum and the  $A_{1g}$  mode is related to the out-of-plane vibration of sulfur atoms.<sup>[19]</sup> The peak difference between these two modes depends on the layer number of MoS<sub>2</sub>. It can be seen that these two modes are located at 384.1 cm<sup>-1</sup> and 404.9 cm<sup>-1</sup>, respectively, with a difference of  $\Delta k = 20.8 \, \mathrm{cm}^{-1}$  ( $\Delta k = A_{1g} - E_{2g}^1$ ), which agrees well with that of the CVD-grown monolayer MoS<sub>2</sub>.<sup>[7-10,18-20]</sup> Also, the PL spectrum of the MoS<sub>2</sub> thin film is measured as shown in Fig. 2(f). The sharp peak is located at 1.87 eV, which is consistent with the band gap of the monolayer MoS<sub>2</sub>.

Fig. 2. (a) Optical image of MoS<sub>2</sub> triangular islands, (b) SEM image of MoS<sub>2</sub> triangular islands, (c) AFM image of the MoS<sub>2</sub> triangular islands, (d) its step height along the black line in (c), (e) Raman spectrum and (f) PL spectrum of MoS<sub>2</sub> triangular island.

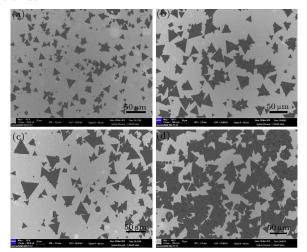

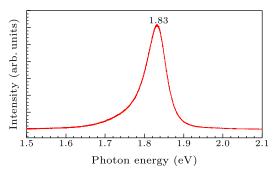

In fact, the monolayer  $MoS_2$  needs a process from nucleation to growth. Figure 3 shows the SEM images of  $MoS_2$  thin films grown on  $SiO_2/Si$  substrates at different Mo precursor temperatures of 720°C, 740°C, 760°C and 780°C. In all cases, the shape of most  $MoS_2$ thin films is triangular and their sizes become gradually larger as the temperature increases from 720°C to 760°C. Actually, the growth of the triangular MoS<sub>2</sub> requires sufficient sulfur atmosphere. [8,13,15,20] Cheng et al. reported that the MoS<sub>2</sub> thin film with a triangle shape is usually developed when the growth rate of Mo-zz is at least three times faster than that of S-zz in the initial hexagonal nuclei.<sup>[21]</sup> The relatively low growth temperatures (720°C, 740°C, 760°C) lead to an S-rich atmosphere (Mo:S < 1:2), so that the MoS<sub>2</sub> thin film grows into a triangle shape. As the Mo precursor temperature increases, more unsaturated Mo atoms can be provided and have higher probability of meeting and bonding with free S atoms in the S-sufficient atmosphere, which is beneficial for the growth of largesize MoS<sub>2</sub> triangular islands. The size of the triangles is  $\sim 30 \, \mu \mathrm{m}$  at  $720 \, ^{\circ}\mathrm{C}$  (Fig. 3(a)) and  $\sim 50 \, \mu \mathrm{m}$  at 740°C (Fig. 3(b)), while at 760°C (Fig. 3(c)), the size reaches more than 120 µm. When the temperature is increased to  $780^{\circ}$ C (Fig. 3(d)), the MoS<sub>2</sub> triangles start stacking and their shape is changed from a triangle to a truncated triangle. According to Ref. [20] to grow  $MoS_2$  by the CVD method,  $MoO_3$  should firstly be reduced to volatile  $MoO_{3-x}$  by S molecules:  $MoO_3+(x/2)S \rightarrow MoO_{3-x}+(x/2)SO_2$ . At a relatively high growth temperature, a great amount of  $MoO_{3-x}$ (Mo:S > 1:2) is produced according to the above equation, resulting in the reaction in a relatively S-deficient atmosphere. This increase of  $MoO_{3-x}$  not only causes the shape evolution but also explains the development of a merged state in the  $MoS_2$  thin film. Figure 4 shows the PL spectrum of the truncated triangular MoS<sub>2</sub> thin film, and an obvious left shift of the peak relative to the monolayer can be seen, which is located at 1.83 eV, implying the increase of MoS<sub>2</sub> thickness. The above results suggest that the Mo source temperature plays a key role in CVD MoS<sub>2</sub> growth, since different temperatures provide different amounts of precursors. At lower temperatures of <760°C, the Mo precursor temperature can be appropriately raised to increase the amount of the Mo source, which is conducive to the formation of large-size MoS<sub>2</sub> triangular islands.

Fig. 3. SEM images of  $MoS_2$  triangles synthesized on  $SiO_2/Si$  substrates with Mo precursor temperature at (a) 720°C, (b) 740°C, (c) 760°C, and (d) 780°C.

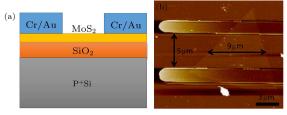

The above as-grown monolayers of MoS<sub>2</sub> are used to fabricate back-gated transistors to evaluate its electrical properties. Figure 5(a) shows the cross-sectional diagram of the MoS<sub>2</sub> field-effect transistors (FETs) and Fig. 5(b) is an AFM image of the drawn transistor on the MoS<sub>2</sub> triangular islands with a channel width/length of  $W/L = 9 \,\mu\text{m}/5 \,\mu\text{m}$  (W is an average value). The source/drain (S/D) regions are completely covered by the contacted metals, and the 3-nm-thick thermal SiO<sub>2</sub> acts as the gate dielectric. Gate bias is applied to the p<sup>+</sup>-Si substrate to modulate the

device, and electrical measurements are conducted under a light-tight and electrically shielded condition at room temperature.

Fig. 4. PL spectrum of the truncated triangular  $MoS_2$  thin film.

Fig. 5. (a) Structural diagram of the back-gated  $MoS_2$  transistor and (b) AFM image of the transistor fabricated on the triangular  $MoS_2$  island.

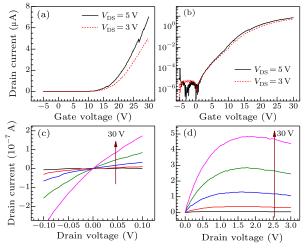

Figures 6(a) and 6(b) show the transfer characteristic (drain current  $(I_{dS})$  versus gate voltage  $(V_{G})$ ) at  $V_{\rm dS} = 3\,{\rm V}$  and  $5\,{\rm V}$  in linear and semi-logarithmic scales, respectively, for the transistor with monolayer  $MoS_2$  as the channel grown at 760°C. The device exhibits a low-off current  $(10^{-12} \,\mathrm{A})$  with an on/off current ratio up to  $10^6$ . Figures 6(c) and 6(d) exhibit the output characteristic curves of the MoS<sub>2</sub> transistor under small  $V_{\rm dS}$  from -0.1 to +0.1 V and large  $V_{\rm dS}$  up to 3 V to demonstrate its linearity and driving capability, respectively. It can be seen that an approximate linear relationship between  $I_{\rm dS}$  and  $V_{\rm dS}$  is observed when  $V_{\rm dS}$  changes from  $-0.1\,\rm V$  to  $0.1\,\rm V$  for  $V_{\rm G}$  from 18 V to 30 V, indicating a non-ideal ohmic contact between the metal and  $MoS_2$ . An unavoidable problem in the CVD MoS<sub>2</sub> is that the incomplete reacted MoO<sub>3</sub> may remain on the MoS<sub>2</sub> thin films when the CVD stops, which increases contact resistance and leads to a non-ideal ohmic contact. In addition, some deep traps between the as-grown  $MoS_2$  and  $SiO_2$  could be introduced, which could capture some electrons in the channel as  $V_{\rm dS}$  increases and induces current collapse phenomena, [22] e.g. negative differential resistance effect, as shown in Fig. 6(d). The carrier mobility of the back-gated MoS<sub>2</sub> FETs was extracted using the formula  $\mu = (\Delta I_{\rm dS}/\Delta V_{\rm G}) \times (L/WC_{\rm ox}V_{\rm dS})$ , where  $C_{\rm ox}$  is the gate capacitance per unit area, and  $\Delta I_{\rm dS}/\Delta V_{\rm G}$  is the slope of the transfer curve in the linear region. The field-effect mobility of the as-grown MoS<sub>2</sub> transistor is calculated to be  $1.92\,\mathrm{cm^2/Vs}$ , which is a low value due to the large S/D contact resistances, as mentioned above. In addition, the extracted subthreshold swing (SS) has a relatively small value of 194.6 mV/dec. The electrical properties of other transistors with monolayer MoS<sub>2</sub> grown at 720°C or 740°C are summarized in Table 1. Obviously, the transistor with monolayer MoS<sub>2</sub> grown at 760°C has the best electrical performance. It is worth noting that the electrical properties of the fabricated MoS<sub>2</sub> transistors, e.g. saturation current and carrier mobility, are not better than those reported in previous reports.<sup>[23–26]</sup> Except for the large S/D contact resistances, other causes probably include poorer interface quality between the MoS<sub>2</sub> and gate dielectric, and increased gate leakage due to the deterioration of the SiO<sub>2</sub> gate dielectric during the MoS<sub>2</sub> growth. Therefore, the S/D contact and interfacial optimizations are important in the future, and a transfer of the as-grown MoS<sub>2</sub> is also needed to obtain better device performances.

Transfer characteristics of the as-grown MoS<sub>2</sub> transistor: (a) in linear scale and (b) in logarithmic scales  $(V_{\rm dS}=3\,{\rm V} \ {\rm and} \ 5\,{\rm V} \ {\rm respectively})$ . Output characteristics of the as-grown MoS<sub>2</sub> transistor: (c) small range of  $V_{

m dS}$ from  $-0.1\,\mathrm{V}$  to  $0.1\,\mathrm{V}$  and (d) large range of  $V_{\mathrm{dS}}$  from  $0\,\mathrm{V}$  to  $3\,\mathrm{V}$  ( $V_{\mathrm{G}}$  from  $18\,\mathrm{V}$  to  $30\,\mathrm{V}$  with a step of  $3\,\mathrm{V}$ ).

Table 1. Performance of devices with different size monolayer MoS<sub>2</sub> as channel grown at different temperatures.

| Temperature   | Mobility         | SS       | On/off ratio |

|---------------|------------------|----------|--------------|

|               | $({ m cm^2/Vs})$ | (mV/dec) |              |

| 720°C (10 μm) | 0.24             | 464.2    | $10^{6}$     |

| 740°C (15 μm) | 0.57             | 272.5    | $10^{6}$     |

| 760°C (20 μm) | 1.92             | 194.6    | $10^{6}$     |

In summary, the effects of the Mo precursor temperature on the size and shape of MoS<sub>2</sub> thin film have been investigated for CVD  $MoS_2$ . It is found that as the Mo precursor temperature rises from 720°C to 760°C, the size of the MoS<sub>2</sub> triangular islands gradually increases up to over 120 µm, to a maximum of 146 μm. When the temperature reaches 780°C, the shape and thickness of the MoS<sub>2</sub> thin film are changed. The involved mechanisms lie in the change of the atomic ratio of S atoms to Mo atoms with the Mo precursor temperature: Mo:S < 1:2 for the temperature range of 720°C−760°C due to the S-rich atmosphere, resulting in the growth of triangular MoS<sub>2</sub> thin film whose size increases as the temperature increases owing to the increased Mo atoms and bonding probability with S atoms, and Mo:S > 1:2 for high temperatures of  $> 760^{\circ}\text{C}$ , e.g.  $780^{\circ}\text{C}$ , due to the S-

deficient atmosphere, leading to the stacking of the triangular MoS<sub>2</sub> islands into truncated triangles. AFM, SEM, Raman and PL spectra are used to characterize the  $MoS_2$  thin film, and confirm its structure and monolayer thickness. Moreover, the as-grown MoS<sub>2</sub> triangular islands are used to fabricate backgated transistors to evaluate their electrical properties. The transistors are n-channel enhancement-mode FETs, where the device with the monolayer MoS<sub>2</sub> grown at 760°C exhibits the best electrical properties: a mobility of 1.92 cm<sup>2</sup>/Vs and a subthreshold swing of 194.6 mV/dec, indicating the feasible approach of fabricating transistors on monolayer MoS<sub>2</sub> grown by the CVD method. Further optimization of growth processing and improvements of the S/D contact and MoS<sub>2</sub>/dielectric interface are needed to obtain excellent electrical performances of the CVD-grown MoS<sub>2</sub> transistors.

## References

- Radisavljevic B et al 2011 Nat. Nanotechnol. 6 147

- Wang X D et al 2015 Adv. Mater. 27 6575

- Lembke D et al 2015 Acc. Chem. Res. 48 100

- [4] Das S et al 2013 Nano Lett. 13 100

- [5] Li H et al 2014 Acc. Chem. Res. 47 1067

[6] Zhan Y J et al 2012 Small 8 966

- [7] Lee Y H, Zhang X Q, Zhang W J, Chang M T, Lin C T, Chang K D, Yu Y C, Wang J T W, Chang C S et al 2012 Adv. Mater. **24** 2320

- Wang S S, Rong Y M, Fan Y, Pacios M, Bhaskaran H, He K and Warner J H 2014 Chem. Mater. 26 6371

- [9] Bergeron H, Sangwan V K, McMorrow J J, Campbell G P, Balla I, Liu X L, Bedzyk M J, Marks T J and Hersam M C 2017 Appl. Phys. Lett. 110 053101

- [10] Heo S, Hayakawa R and Wakayama Y 2017 J. Appl. Phys.

- [11] Wu W, De D, Chang S C, Wang Y, Peng H, Bao J and Pei S S 2013 Appl. Phys. Lett. **102** 142106

- [12] Yang X N et al 2016 Sci. Chin. Mater. 59 182

- Cao Y J, Luo X F, Han S M, Yuan C L, Yang Y, Li Q L, Yu T and Ye S L 2015 Chem. Phys. Lett. 631 30

- Wang W Z, Zeng X B, Wu S X, Zeng Y, Hu Y S, Ding J and Xu S 2017 J. Phys. D 50 395501

Xie Y, Wang Z, Zhan Y J, Zhang P, Wu R X, Jiang T, Wu

- S W, Wang H, Zhao Y, Nan T and Ma X H 2017 Nanotechnology 28 084001

- Zhou J D et al 2018 Nature **556** 355

- [17] Najmaei S, Liu Z, Zhou W, Zou X L, Shi G, Lei S D, Yakobson B I, Idrobo J C, Ajayan P M and Lou J 2013 Nat.

- [18] Wang S S, Pacios M, Bhaskaran H and Warner J H 2016 Nanotechnology 27 085604

- [19] Lee C G, Yan H G, Brus L E, Heinz T F, Hone J and Ryu S 2010 ACS Nano 4 2695

- [20] Yang S Y, Shim G W, Seo S B and Choi S Y 2017 Nano Res. 10 255

- [21] Cheng J X, Jiang T, Ji Q Q, Zhang Y, Li Z M, Shan Y W, Zhang Y F, Gong X G, Liu W T and Wu S W 2015 Adv. Mater. **27** 4069

- Zhu W J et al 2014 Nat. Commun. 5 3087

- Cho W C et al 2016 IEEE Trans. Nanotechnol. 15 2

- Sun L F, Leong W S, Yang S Z, Chisholm M F, Liang S J, Ang L K, Tang Y J, Mao Y W, Kong J and Yang H Y 2017 Adv. Funct. Mater. 27 1605896 [25] Han G H, Kybert N J, Naylor C H, Lee B S, Ping J L, Park

- J H, Kang J, Lee S Y, Lee Y H, Agarwal R and Johnson A T C 2015 Nat. Commun. 6 6128

- [26] Ju M, Liang X Y, Liu J X, Zhou L, Liu Z, Mendes R G and Fu L 2017 Chem. Mater. 29 6095